基于Virtex-5的PCI-Express总线接口设计和实现

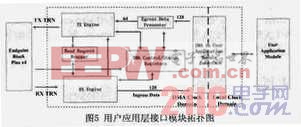

使用LogiCORE产生的Endpoint Block Plus中,定义了两个基地址memory空间,一个用于DMA寄存器的操作,一个用于用户逻辑空间。本文主要介绍的就是用户应用层接口的实现,该接口将通过TRN进行相应的事务层数据包的处理。 TX Engine:该模块主要用于产生和发送事务层数据包:Posted事务包(存储器、I/O、配置读写事务)、non_Posted事务包(该总线事务包分两步进行,首先是发送端向接收端提交总线读写请求,之后接收端再向发送端发送完成包)和completion(完成)包。该模块通过发送posted memory写,non_Posted memory读,和接收completion包来完成DMA的读写请求。该模块的启动由DMA Control/Status Registers模块控制。该模块又包括若干子模块:posted packet generator模块、non posted packet generator模块、completion packet generator模块和transmit TRN state machine模块,上述三个generator模块均由transmit TRN状态机模块控制,该状态机的控制信号来自Endpoint Block Plus核以及DMA Control/StatusRegisters模块。

3 PCI-Express总线接口设计

本文的硬件主要就是单片XC5VLX50T实现PCI-Express总线接口,并在该FPGA内设计具体应用,完成PCI-Express总线接口的测试和使用。本文实现的应用有如下几个特性:

(1)主机通过控制FPGA内部的寄存器文件来启动和停止DMA操作,支持endpoint到root的全双工DMA读写。

(2)使用LogiCORE产生的Endpoint Block Plus进行PCI-Express总线接口设计。该硬核集成了PCIE协议中的物理层、数据链接层的解析,提供传输层接口(TRN)供设计者对相应的事务层数据包的处理。

(3)PCI-Express总线接口支持x4通道的实现,主机操作系统为嵌入式Linux 2.6.10系统。在Windows XP下也进行PCI-Express接口测试。

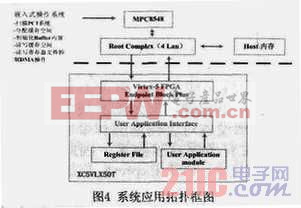

FPGA是整个设计的最关键部分,主要实现:PCI-Express硬核;在硬核的用户接口和传输接口实现PCI-Express传输本地总线的时序逻辑;并且在其内部完成DMA控制时序逻辑。FPGA是PCI-Express总线接口和应用模块数据传输的通道。在Host端使用嵌入式的MPC8548作为主机系统应用CPU,设计相应的驱动和应用程序配合FPGA内部代码的调试。图4为该系统的拓扑框图。

用户应用层接口主要包括如下几个模块:a.TX Engine模块;b.RX Engine模块;c.Egress Data Presenter模块;d.Read Request Wrapper模块;e.DMA Control/Status Registers模块。这几个模块之间的拓扑关系如图5所示。

RX Engine:该模块主要用于接收Endpoint BlockPlus模块从RX TRN接口送出的事务层数据包,对不同的事务包进行解析,根据相应的包做相应的处理,该模块能处理如下三种事务包:完成包、memory读包和memory写包。该模块又包括如下子模块:接收TRN状态机模块、接收TRN监控模块、接收数据状态机模块以及两个fifo用于存放完成包的接收数据和完成包中目的和源的地址以及数据包的长度,用于设置DMA Control/Status Registers模块中的各个状态。接收TRN状态机模块只负责TRN接口处的数据包的状态和接收收据,送给后面的模块;接收TRN监控模块负责根据不同的TLP包来分配数据和状态,是直接将带数据的完成包的数据写到用户应用接口fifo,还是读请求或写请求TLP包通知TX engine,组成相应的包发送出去或者通知DMA控制器进行相应的DMA传送控制;接收数据状态机模块对接收到的数据进行相应的处理。

Egress Data Presenter:该模块是专门为TX Engine模块提供发送数据的模块,要发送到主机的数据都在该模块中进行处理,它和TX Engine模块间的数据位宽定义为64bit。

Read Request Wrapper:该模块主要用于TX Engine模块和RX Engine模块之间的通信控制接口,本文中设计DMA的读写操作每包可能的数据长度为:1KDW、2KDW、3KDW、4KDW、8 KDW、16 KDW之间可选。该选择是由主机通过写寄存器文件来进行长度策略选择的。

DMA Control/Status Register:该模块主要用于主机系统通过控制FPGA内部的寄存器文件的设置来启动和停止endpoint到root的DMA读写操作。包括一个控制寄存器以及若干个配置寄存器,配置寄存器有主机的目的地址、源地址信息,本地的目的地址、源地址信息,以及每次DMA的数据包长度等信息。由控制寄存器中的bit位的状态来启动所有的状态机的控制,所以控制寄存器是整个操作的关键信号。

4 实验结果分析

首先初始化FPGA内部的寄存器文件,通过设置相应的控制位启动数据从Host内存通过PCI-Express接口向下传输到FPGA内部,传输完毕后,FPGA内部控制逻辑将接收的数据进行处理,并得到向上输出的数据,然后通过PCI-Express接口,再将数据传输回Host内存,Host内存的检测程序对所收到的数据进行校验。在进行FPGA内部PCI-Express接口速度测试时,由于Host读写内存需要一定的时间,所以在测试速度时不进行Host内存的读写。而在正确性测试时,则通过Host读写内存判断数据是否正确。所有ChipScope截图均以一包数据包大小为4KDW为例进行捕捉,图中有文字标识其中的信号意义。

图6为Host将数据通过PCI-Express接口向下传输到FPGA内部的ChilpScope截图。

设计 实现 接口 总线 Virtex-5 PCI-Express 基于 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)