基于ADSP-BF533的家庭安全系统设计策略

基于ADSP-BF533的家庭安全系统设计策略

现代传感器技术和网络技术的发展,使得运用现代传感器与计算机技术进行防盗,已成为家庭安全系统发展的必然趋势。文中设计了一种基于ADSP-BF533的家庭安全系统,该系统以BF533为核心处理器,采用MPEG-4视频压缩标准,通过红外探测器检测非法入侵,一旦检测到异常情况,即以短信的形式向用户报警,同时启动视频采集模块获取现场图像信息,并将压缩编码后的视频数据保存到存储设备中,以便用户回放、查看和编辑。与传统的依靠安装防盗门窗的防盗方式和以现场语音报警为手段,以阻吓和告知为目的的报警器相比,本系统具有GSM远程报警和现场图像采集并存储功能,提高了报警的及时陛、可靠性和警情处理的有效性。

1 系统整体方案

基于BF533的家庭安全系统设计方案,主要由4部分组成,分别为热释电红外检测、CMOS图像采集、GSM报警和图像存储。系统结构框图,如图l所示。热释电红外检测模块与BF533的PF口相连,对室内空间进行检测,一旦检测到非法入侵,立即向DSP发送中断请求,将处于睡眠状态的DSP唤醒工作。GSM短信报警模块与UART接口相连,DSP通过UART口可以控制GSM模块使其发送报警信息。CMOS摄像头连接在PPI接口,PPI口以DMA方式将视频数据搬移到SDRAM中,供DSP进行压缩,存储设备SD卡通过SPI接口与DSP连接,用于保存压缩后的视频码流数据。

2 系统硬件设计

2.1 热释电红外检测电路

热释电红外检测模块采用BISS0001型热释电红外控制专用芯片完成。当有人在热释电红外传感器的有效检测区域内活动时,传感器将接收到人体发出的红外信号,并将其转变成微弱的脉冲电压信号,此电压信号经BISS0001内部电路放大、鉴幅处理及定时控制后,从输出引脚输出高电平,该高电平连接到DSP的PF口,作为DSP的中断请求信号,唤醒DSP进人工作状态。

2.2 CMOS图像采集电路

本系统采用Pixelplus公司的P03030K图像传感器完成图像采集功能,P03030K输出30万像素图像,支持多种输出模式和输出数据格式,此处采用QVGA输出模式和YUV4:2:2输出数据格式。P03030K与BF533的PPI口相连接,连接方式,如图2所示,P03030K产生HREF,VSYNC,PCLK这3种同步信号,分别为行同步输出信号、场同步输出信号和输出像素时钟。Y[7:0]为P03030K输出的图像数据信号。BF533使用GPIO的PF0和PF1模拟I2C总线协议,从而实现对P03030K内部寄存器的读写操作。

2.3 GSM报警电路

GSM报警电路采用西门子公司的TC35模块完成,TC35模块通过MAX232串口接口芯片与DSP的UART口相连接。TC35模块还提供了SIM卡接口,

插入注册后的SIM卡,便能够接入GSM通信网完成短信报警功能。

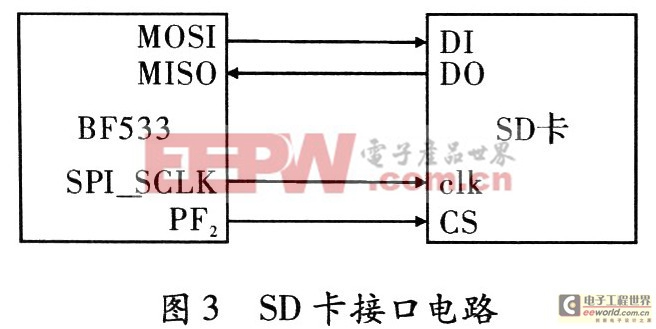

2.4 图像存储电路

本系统采用SD卡存储压缩编码后的视频数据,SD卡有两种工作模式:SDIO模式和SPI模式。由于BF533支持SPI接口,故采用SPI模式。BF533的SPI接口数据传输速率最快可达到系统时钟的1/4,按系统时钟为118.8 MHz进行计算,SPI的最高数据率可达到29.7 MB/s,考虑到视频流数据量较大,采用双缓冲机制进行存储,能够满足系统要求。SD卡接口电路,如图3所示。

3 系统软件设计

系统软件可分为视频采集及压缩程序、GSM短信报警程序和图像存储程序3部分,软件流程图,如图4所示。

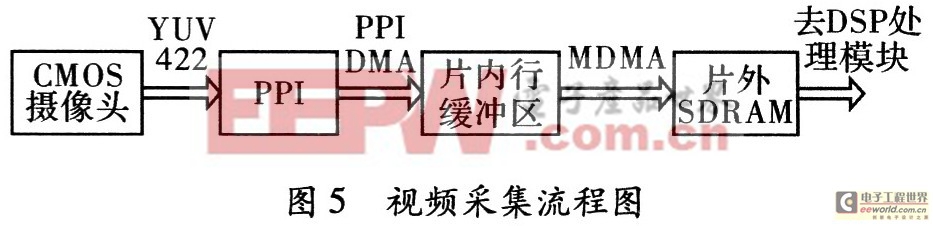

3.1 视频采集及压缩程序

DSP通过I2C接口完成对P03030K图像传感器的初始化,并设置相应的寄存器完成对工作模式、数据输出格式、分辨率、亮度和色度等的设置。P03030K与DSP的PPI口相连,输出图像数据以DMA方式传输到SDRAM中存储,本系统采用乒乓缓冲区的方法传输数据,在内存中开辟两个缓冲区,使用两个头尾相连的描述符链表控制PPI DMA一次传输数据到两个缓冲区中。DMA每采集完一行图像数据之后就产生一次中断,在中断服务程序中使用存储器DMA将数据搬移到片外SDRAM,等待DSP对其进行MPEG-4压缩处理。视频采集流程图,如图5所示。

DSP对视频数据进行压缩编码时采用MPEG-4标准,由于CMOS图像采集模块输出YUV4:2:2图像,而编码模型的输入为YUV4:2:0图像,故需要对采集到的图像进行色度重采样。DCT和IDCT是编码过程中被频繁调用的两个函数,故采用汇编语言实现且使用Chen的快速算法,此外根据BF533的硬件和编译系统的特点,运用各种方法对MPEG-4编码程序代码进行大量的优化工作,利用循环缓冲技术和DSP提供的各种像素操作指令和向量操作指令对PADDING算法、运动矢量预测、SAD最小搜索算法和半像素内插等需要反复执行的过程进行汇编优化,充分发挥BF533的并行处理能力。在内存分配方面,在SDRAM中开辟了4个帧缓冲器,分别用于保存当前编码帧、当前参考帧、下一编码帧和下一参考帧数据。DSP的片内RAM容量较小,但是访问速度较快,而MPEG-4的最小编码单元是宏块,所以可以将宏块从片外SDRAM转移到片内RAM中进行处理,处理结束后再存到SDRAM中。另外为了加快数据块搬移速度,充分利用BF533强大的DMA能力完成数据传输操作,同时将CPU频繁访问的程序和数据放在片上缓存中,并充分利用乒乓缓冲结构,提高编码效率。

MPEG-4编码流程,如图6所示。

ADSP-BF533 相关文章:

- ADSP-BF533在低耗高速实时系统中的应用(03-08)

- 基于ADSP-BF533的家庭安全系统设计(03-26)

- 基于ADSP-BF533在低耗高速实时系统中的应用(05-04)

- 基于ADSP-BF533的数字通信信号发生器设计(04-28)

- 基于ADSP-BF533的MPEG-4实时编码器实现(06-13)

- 基于ADSP-BF533的MPEG-4实时编码器系统实现(07-08)