基于ADSP-BF533的MPEG-4实时编码器系统实现

引言

MPEG-4视频编码技术可以在较小的带宽下传输高质量的视频数据,节省大量存储空间,但编码复杂度也较高,目前丰要有3种实现方案:在通用PC上编程实现;通过ASIC硬件实现以及使用通用DSP芯片实现。与前两者相比,通用DSP芯片实现方案具有以下优势:运算性能强;可升级性好,与PC类似,通用DSP芯片的功能仍是通过编程来实现的,能快速、方便地进行软件升级及添加新的功能,以适应技术发展和市场变化;成本低、功耗低、适应场合广泛。

系统硬件设计

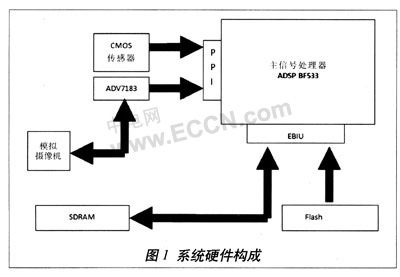

编码系统处理核心为ADSP-BF533(以下简称BF533),利用其多功能并行接口PPI采集视频数据,该PPI具有DMA功能,无需内核干预便可进行高速数据传输,传输完成后可自动向内核发出DMA中断。

视频采集部分选用0mniVision公司的CIF级彩色CMOS图像传感芯片OV6630,其最大分辨率为352×288,采集速率最高可达60fps,且片内硬件实现了原始RGB数据到4:2:2YUV格式数据的转换,用户无需自行编写复杂的RGB转YUV应用程序,大大减少了代码量,很适合用作MPEG-4编码。

设置OV6630输出为4:2:2 YUV视频数据格式,BF533的PPI即可直接接收该格式视频数据。二者可实现无缝连接,无需中间电路。

考虑到目前还有大量模拟制式的摄像机仍在广泛应用,系统中还增加了视频ADC ADV7183,该芯片可以把PAL制模拟电视信号转为ITU-R656标准4:2:2格式数字视频,同样将ADV7183输出端口与BF533的PPI相连。这样,既可以采用系统自带CMOS图像传感器采集视频,也可以外接PAL制模拟摄像机,用户可自由选择。

由于BF533片内存储空间有限,而视频采集、编码数据量巨大,选用一片Hynix公司的4MBSDRAM HY57V56162(内含4个内部子集)作为BF533片外大容量动态存储器。同时,为存放程序启动代码,利用一片容量为1MB的闪存芯片PSD4256G6V构成BF533的片外非易失性存储器。系统硬件构成如图1所示。

编码器设计实现

存储器空间分配

BF533采用统一的32位、共4GB可寻址空间,包括位于片内的L1高速SRAM,片外的同步存储器空间SDRAMSpace,以及异步存储器空间(A syn chronousMemory Space)。

片内Ll SRAM包括:64KB指令SRAM、16KB指令Cache/SRAM、32KB数据SRAM、32KB数据Cache/SRAM,以及4KB便签存储器。

L1 SRAM工作在内核时钟频率,内核可以对其进行高速带宽访问。它是所有存储器中访问速度最快的,但容量有限,因此,只应将那些最关键的代码和数据存放在L1SRAM里。同时,指令Cache和数据Cache全部使能,这样可以大大提高访问片外存储器的效率。Cache设置是通过相应的I M E M_C O N T R O L、DMEM_CONTROL,以及CPLB寄存器配置实现的。

由于BF533片内存储空间有限,而原始视频数据量较大:CIF级4:2:2格式每帧图像占用的空间为202752字节,如果采用模拟PAL制式视频输入,每帧占用空间更是高达829440字节,只能将其放至SDRAM中。同样,视频编码数据也应存放在SDRAM中。此外,系统启动完成Boot loader引导后,主要关键代码放在片内L1程序SRAM中执行,但大部分程序代码仍需从SDRAM中执行。由于SDRAM特殊的读/写方式,如果下次访问内存页与当前活动页(Active Page)不同,即出现了页错失(Page Miss),SDRAM就必须首先关闭当前页,再打开新的页,大大降低了SDRAM读写速率。而该系统中SDRAM又需存储多种数据,内核、DMA均需要频繁访问SDRAM,因此,应精心分配SDRAM空间,以使页错失现象尽量少发生。

BF533的SDRAM控制器(SDC)可以支持SDRAM每个内部子集中的一个活动页,且在这4个I-Bank中进行切换时无需任何延迟。这样,将不同的数据、代码映射至不同的I-Bank,可使页错失现象降到最少,进而改善访问SDRAM的效率。

由于需要实时编码,为保证视频采集和压缩可以同步执行,采用乒乓缓冲技术:设置了两块视频帧接收缓冲区BUF1和BUF2,采用BF533的DMA传输链方式进行传输。当某一DMA缓冲区填满后,内核对其作MPEG-4编码(同时也在构建参考帧),此时DMA开始对另一块缓冲区进行填充。由于BUF1、BUF2、程序代码以及参考帧均位于不同的I-Bank,减少了SDRAM页面切换的机会,实现了对SDRAM的高效访问。

MPEG-4程序流程

MPEG-4编码是基于宏块(Macro Block)进行的,每个宏块包含4个8×8亮度子块和2个8×8色度子块。MPEG-4编码原理主要包括对I帧和P帧的编码,P帧比I帧多出了运动估计和补偿模块,二者编码流程如图2所示。

代码编写及优化

BF533支持C/C++高级语言,但高级语言执行效率较低,为达到最大执行效率,采用全汇编语言实现MPEG-4编码。

对于I帧编码,主要的运算量是前向离散余弦变换FDCT和反向离散余弦

ADSP-BF533 MPEG-4 实时编码器 相关文章:

- ADSP-BF533在低耗高速实时系统中的应用(03-08)

- 基于ADSP-BF533的家庭安全系统设计(03-26)

- 基于ADSP-BF533在低耗高速实时系统中的应用(05-04)

- 基于ADSP-BF533的数字通信信号发生器设计(04-28)

- 基于ADSP-BF533的MPEG-4实时编码器实现(06-13)

- 基于ADSP-BF533的μClinux嵌入式系统移植与开发(09-06)