一种用于数字下变频的高阶分布式FIR滤波器及FPGA实现

时间:04-29

来源:互联网

点击:

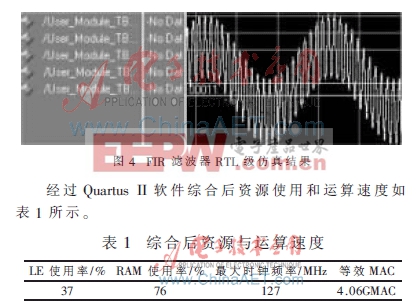

由表1可知,在LE的使用率仅为37%时,RAM的使用率已达76%,还有较多的LE未被使用。可在随后的工作中进一步改进设计方案,采用超前进位加法等方法缩短关键路径,进一步提高滤波器的运算速度。

本文对分布式滤波算法进行了详细的分析和推导,通过公式变形阐述了提高电路运算速度和减小存储器资源消耗的方法。通过理论推导和对Cyclone III系列的FPGA中嵌入的存储器块的分析,设计了一种适用于EP3C40F484C6N芯片的高阶分布式FIR滤波器实现方案并进行了仿真和综合。结果表明,采用该方案可以实现高阶的FIR滤波器设计并得到很高的等效乘加运算速度。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)