一种改进的图像重组算法及其硬件实现

的方式,即一个范围内的D值对应一个E值,只要所设的值能达到“D大则E小”的效果便可;

②求D时所需的除以21/2的运算可转化成近似移位相加。

4.硬件实现

本算法涉及了大量的算术运算,而且计算中像素相关性的要求需要存储大量像素,所以硬件实现必须适当减少硬件资源和RAM的使用量,从而降低ASIC的面积,本文提出如下的解决方法。

4.1 流水线式的运算处理

由式(1)、式(2)可见,计算插入的R、G、B值要经过大量的运算,而传感器送过来的数据是实时的,对其处理也必须是实时的,也就是说进来像素的分量值就要送出一个像素的R、G、B值。假设模块的主频率和传感器送来的数据频率分别为48MHz和12MHz,则在四个周期就要输出一个像素的R、G、B值。显然,四个48MHz时钟周期是不可能完成如此多的运算的。

本文采用的方法是把众多运算分成m个步骤完成,而每个步骤都占n个周期,一个步骤完成的结果在下一个n个周期运用计算,如此一级一级的计算,输入与输出都是实时的,其设计思想近似于计算机架构中的流水线结构。其中m和n要根据模块时钟与传感器输出数据的频率的比例关系以及所设计ASIC的工艺水平对时序的限制来确定。此方法可使此模块面积减为原始设计的1/2左右。以计算R[5,5](像素坐标如图1)为例:步骤1:求得G[4,3],G[4,5],G[6,3],G[6,5],G[4,7],G[6,7];步骤2:求得R[5,4]和R[5,6];步骤3:求得R[5,5],这样,每个步骤都有4个周期去完成,就可以满足模块的实时性。其中步骤1可再分为前两个周期计算G[4,3],G[4,5]和G[6,3],后两个周期计算G[6,5],G[4,7],G[6,7],从而复用其中除法器、加法器和乘法器,使该运算占用资源减少到一半。同样道理,计算R[5,4]和R[5,6]时也可以复用资源,分别在两个周期内完成其运算。

4.2 堆栈式的RAM操作

此算法要求存储9×9窗口大小的像素信息,也就是要存下9行的传感器送来的数据。本文提出的方法只需要存8行的像素信息即可,但要配合一个9×9的寄存器阵列实现。下面以实例说明RAM操作过程:当第9行数据要送来时,前8行数据已按顺序存储在RAM中。当传感器送来G[1,9]时,模块要进行以下工作:(1)把RAM第1列数据读出;(2)然后把第1列后7行的数据连同G[1,9]写到RAM的第1列中,同时把第1列全部数据连同G[1,9]写到9x9的阵列的第一列中,这样既保存了第1行的数据,又保证第9行数据能写到RAM里,相当于将RAM数据往里推,丢去第1行数据,推入第9行的数据。如此类推,就可以减少一行存储资源。

5.仿真与验证

本文基于摄像头控制器芯片的开发平台进行了仿真验证,并比较了改进的算法与传统算法的优劣。

此模块通过了功能仿真、DC工具时序、面积等分析,并在FPGA板上通过接传感器,经JPEP压缩,由USB传输到计算机验证其效果。本文采用Syn-opsys公司的DC compiler分析了各算法实现的面积代价。同时,本文针对几种算法的图像还原能力作了分析:用线性方法、kimmel方法和本算法处理同一张图片转化的bayer格式图片,设R(x,y)为原图像素值,r(x,y)为处理后像素值:

设满足(3)式的点为还原良好点,其个数为n,本文所用测试图片为640×480大小,令h=n/640×480为算法的还原程度判断。

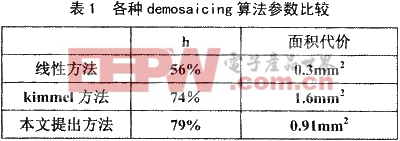

图5和表1是几种Demosaicing算法的仿真结果图片及其相应的h值和面积代价,可以看到本文提出的方法的图像质量要比其他算法的好,尤其在高频时,混淆现象得到了很好的改善。

6 结论

本文在详细分析传统算法的优劣基础上,提出了新的图象重组算法,而流水线式分时复用资源的实现方法节省了接近一半的资源,很好地克服了模块实时性要求,主频时钟限制和demosaicing算法复杂性带给硬件实现资源成本高的问题。

- 基于算法的DSP硬件结构分析(04-02)

- 电力电子装置控制系统的DSP设计方案(04-08)

- LPC2292的μC/OS-II硬件抽象层构建(04-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 基于DSP和IPM的变频调速系统的硬件设计(11-25)