针对DES密码芯片的CPA攻击仿真设计方案

具有相关性或仅有弱相关性,其相关系数很校根据这一原理,可以用仿真的方法对密码算法电路进行攻击,根据攻击的难度可以判断抗功耗分析性能。

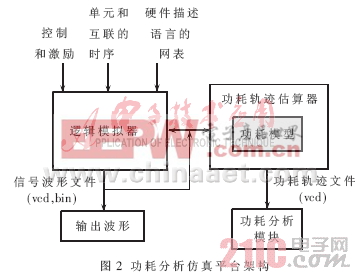

3 功耗分析仿真平台

在系统的设计阶段,人们大多利用计算机进行数学仿真实验,因为修改、变换模型比较方便和经济。在部件研制阶段,可用已研制的实际部件或子系统去代替部分计算机仿真模型进行半实物仿真实验,以提高仿真实验的可信度。在个别情况下,可进行全物理的仿真实验,这时计算机仿真模型全部被物理模型或实物所代替。

建立的仿真平台如图2所示。仿真平台主要由逻辑模拟器、功耗估算器和功耗分析模块组成。框图中应用Mentor公司提供的ModelSim作为逻辑模拟器,逻辑模拟器输入有:所设计密码电路的硬件语言描述代码、电路的激励文件和一些反标延迟信息等。输出的密码电路的功耗仿真结果是以vcd格式存储的文本文件,这个vcd文件包含了所有的信号模拟变化以及相应的仿真时刻标签,然后用VisualC++对vcd文本文件进行处理,得到模拟功耗数据,最后用MatLab对模拟功耗数据进行统计分析,推测密钥信息。

要统计DES密码芯片中每个时钟周期的模拟功耗值,可以通过统计关键寄存器中在相邻时钟周期内0、1的变化情况。根据式(2)所示已经建立的功耗模型,将电路所处理的数据变化转换为模拟功耗变化即可。

4 DES算法的CPA攻击仿真及结果分析

基于所建立的功耗分析仿真平台,结合分组密码算法DES算法进行功耗分析攻击实验。下面是CPA攻击的详细步骤及结果分析。

(1)用仿真的方法进行攻击的第1步是产生1个仿真功耗文件

任意选择1 000个随机明文和1个固定但随机的密钥。每轮加密之后,记录下寄存器中数据二进制序列的变化情况,根据建立的功耗泄漏模型,统计模拟功耗值。这样仿真器就产生1个包含N×16的矩阵M1。

(2)选择寄存器中M个最高位,用与步骤(1)相同的明文及密钥进行仿真实验

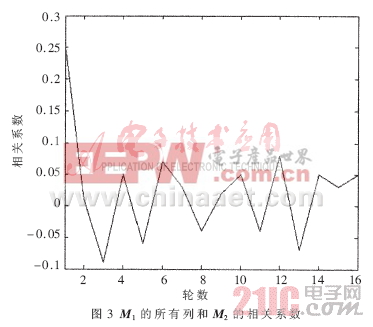

仿真器统计寄存器中位的变化数目,结果存储在矩阵1 000×1的矩阵M2中,在这个验证实验中,选择M为8,然后计算M1的所有列和M2的相关系数,如下:

ci=C(M1(1:1000,1),M2) (7)

式中,i=1,…10, M1(1:1000), i代表矩阵M1的第i列向量。步骤(1)和步骤(2)都用了同样的明文的密钥,所不同的是它们考虑的位变化的数目不同。第(2)步产生的值是第(1)步初始化密钥加操作计算值的预测。如果计算是正确的,M2和M1的第一列的相关系数比其他列要高得多。图3为预测的情况。

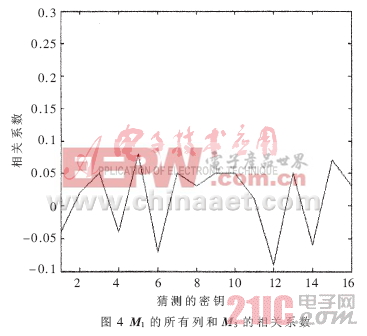

(3)重复步骤(2),但使用一个不同的密钥

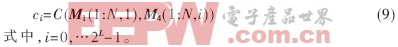

这时产生1个功耗文件矩阵M3。与第(2)步一样计算M3和M1所有列的相关系数:

式中,i=1,…10。由于实验中使用了一个不同的密钥产生M3,所以M3和M1所有列的相关系数将是很小的(或者说是没有相关性),包括第1列。通过计算得出如图4所示的相关系数图,图中的曲线表明其结果和预测的相同。

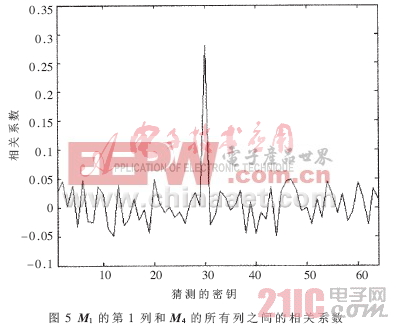

(4)对所有8 bit密钥组合进行实验

对这个实验进行拓展,对密钥的最高L=8比特所有可能性进行猜测,也就是对这8 bit进行强力攻击,这样就能产生1个1 000×2L的矩阵M4。8 bit密钥组合中必有一个是正确的密钥,而且只有这个密钥计算出的第1轮功耗变化与第1轮是统计相关的(相关系数比较大),由此可以通过这种方法推测出密钥。图5为M1的第1列和M4的所有列之间的相关系数。从图中可以看出,所猜测的密钥只有1Ahex=30dec时具有较高的相关性,所以正确的密钥是(30)dec。

式中,i=0,…2L-1。

通过功耗仿真的方法可以对DES密码芯片进行成功的攻击,根据攻击的难度大小,也就是所得到的相关系数的大小,可以判断一个密码芯片抗功耗分析攻击能力的大小,这样就能够在设计阶段评估密码芯片的抗功耗分析攻击的能力大小,为密码芯片设计者提供参考,以便及时添加相应的抗功耗分析的防御措施。

抗功耗分析性能的评估标准在很多文献中只是简单提到过,且没有统一的标准。本文中采用了KrisTri所用的评估标准MTD(Measurements To Disclosure),也就是对于某个密码芯片来说,能够破解1 bit密钥所需要的随机明文数目。本文模拟攻击过程也可以用这种标准来衡量密码芯片的抗功耗分析性能。

为研究密码芯片的抗功耗分析性能,搭建了功耗分析仿真平台,并结合DES分组加密算法进行了相关性功耗分析攻击实验。实验结果表明,搭建的仿真平台是有效的,且说明未经过防御的DES算法容易受到相关性功耗分析的威胁。

仿真 设计 方案 攻击 CPA DES 密码 芯片 针对 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 数字频率合成器的FPGA实现(08-07)

- 基于DSP的导弹仿真器嵌入式组件设计(04-30)

- 如何将DSP和MCU两者完美结合(08-10)

- 高性能仿真器与开发包加速普及DSP应用开发(11-22)

- 基于DSP内嵌PCI总线的卫星信号仿真器设计(04-17)