基于FPGA的智能仪器远程控制系统

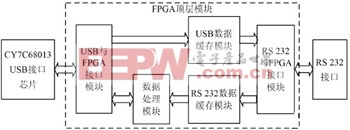

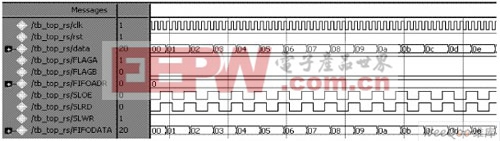

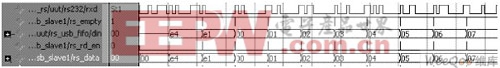

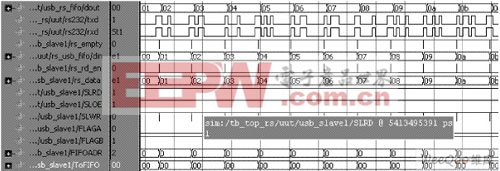

向OUT FIFO,进入准备读数据态;在准备读数据态,如FIFO空,在本状态等待,否则进入读数据态;在读数据态,使SLOE,SLRD有效,从数据线上读数,再使SLRD无效,以递增FIFO读指针,再使SLOE无效,进入读取后状态;在读取后状态,如需传输更多的数,进入准备读数据态,否则进入空闲态。 USB数据缓存模块:用来缓存计算机发给智能仪器的指令等信息。是由FPGA芯片的IP核生成的先入先出存储器FIFO。容量为8b*512depth。占用1个块RAM资源。 RS232数据缓存模块:用来缓存由智能仪器发出的数据。是由FPGA IP核生成的先入先出存储器FIFO。容量为8b*512depth,占用1个块RAM资源。 RS232与FPGA接口模块:RS232与FPGA之间的接口转换模块。主要功能为进行串/并和并/串转换。 将USB数据缓存模块中缓存的内容以合适的速率通过串口发给智能仪器,并将智能仪器发出的数据缓存到RS232数据缓存模块中。此模块也是由两个状态机实现。串口通信必须要设定波特率,这里采用的波特率为9600Kb/s,采用的时钟为50MHz,相当于传送1位数据需要约5028个时钟周期,这里采用减法计数器来控制,即计数器计到5028个时钟周期后,就开始传输下一位数据。 数据处理模块:主要功能为根据上位机的指令对RS232数据缓存中的数据做出相应的处理。处理后再向上位机传。主要的处理方式有定时取数、平滑处理等。实现方式由状态机等实现。FPGA顶层模块:主要负责各模块间数据流的流向。以及与外部芯片相连的输入输出信号的定义。 系统在工作时,在采集数据上传上位机时,数据通道为:智能仪器发送的数据通过RS232接口模块存在RS232数据缓存模块中缓存。当缓存到一定的数据量后,再通过数据处理模块连续的读取FIFO中的数据并根据上位机发送的命令进行相应的数据处理,然后将处理的数据通过USB与FPGA接口模块传给USB接口。在上位机下发控制命令时,数据通道为:上位机发送的命令通过USB口传给FPGA的RS232与FPGA接口模块,此模块判断是数据处理指令还是控制仪器指令。如果是数据处理指令,则传向数据处理模块让其按要求进行数据处理。如果是控制仪器指令,则将其存入USB数据缓存模块中,再由RS232与FPGA接口模块读取,转成RS2322格式后传出。由于RS232接口速度比USB接口慢,用FPGA内部的异步时钟FIFO解决速率匹配问题。 将通过RS232传过来的数据缓存在FIFO中,然后存到一定数据量后再全部连续的取出,如此往复,从而实现数据的连续采集及上位机的实时显示。将通过USB传过来的数据放在另一个FIFO中缓存,让FPGA按照RS232的速率进行读取。这样可以防止RS232的速度跟不上USB的速度而产生的数据丢失。 3 仿真结果 FPGA采用的系统时钟频率为50MHz,仿真工具为Modelsim SE 6.5a,仿真用数据为连续的8b数据。 仿真结果如图4所示。 图4为FPGA读USB内部FIFO的仿真结果,DATA为模拟从USB口接到的数据,该数据已存在于USB芯片的FIFO中。FIFO DATA为FPGA接到的数据,由上可以看出,FPGA可以将USB接受到的数据解析出来。 图5为RS232与FPGA接口部分仿真结果。可以看出,由RS232接收串行数据RXD已经转换为并行数据din。程序中是在一个有效字节结束后将其存入FIFO中,由图可以验证。图6顶层模块仿真图,为了验证由FPGA发出的数据能正确的接受到,先由FPGA内部发数据,然后通过RS232的TXD端口发出,让RXD与TXD相连再接收,可以看出发出的数据可以被正确的接收回来并传向USB接口,说明时序正确。 同理可以验证USB端的收发时序。 4 结 语 本文采用FPGA实现了USB与RS232间的接口转换及数据处理的功能。设计中先入先出存储器的运用解决了数据的缓存的和速率匹配问题,有限状态机的运用使得程序设计更加清晰可靠。该设计将复杂的信号运算集中在FPGA中完成,利用FPGA独特的并行处理能力,减小上位机工作量的同时,提高了系统运行速度。

图3 FPGA总体设计框图

图4 FPGA读USB内部FIFO仿真图

图5 RS232接收端仿真图

图6 顶层模块仿真图

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)