在FPGA中实现图像格式转换的参考设计

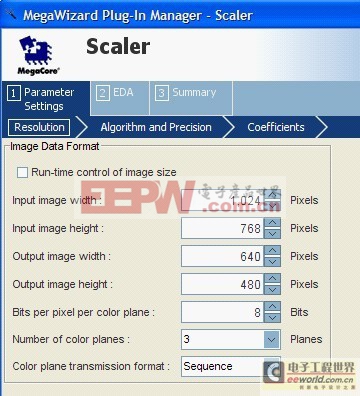

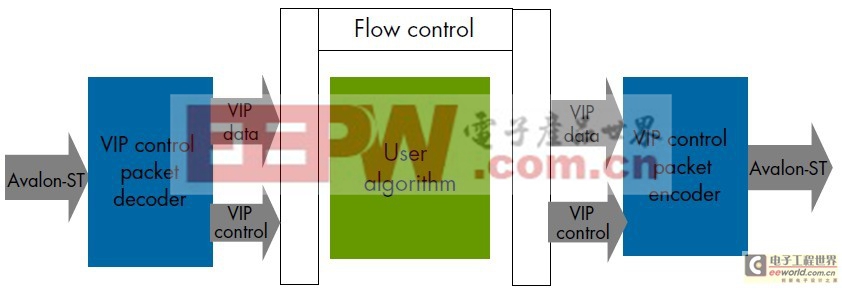

个纵向抽头) 的多相算法对逐行视频流进行缩放。 采用Avalon 存储器映射(Avalon-MM) 从机控制接口对缩放器进行配置,支持缩放器输出分辨率运行时规范要求。此外,当缩放比率变化时, Nios? II 处理器上运行的软件计算并重新装入合适的系数,从而提高了图像质量。最后,在将视频流与背景测试码型以及第二个视频流混合之前,帧缓冲功能在外部存储器中缓冲视频数据。两路视频流输入到合成器进行缩放和同步,需要对突发数据流进行平滑处理。 第二个通道处理质量稍差,这样可以提高视频格式转换的资源利用率。主要有两种方法来处理两路不同格式的视频流: ■ 使用简单的最近邻居缩放算法对第二个视频流进行缩放,需要较少的片内存储器和乘法器资源。 ■ 使用场合并去隔行算法对第二个视频流进行去隔行处理,需要较少的逻辑资源和外部存储器带宽。 3 定制您的图像格式转换设计 Altera 视频工作台从根本上支持用户定制设计。工作台支持三级定制,非常灵活,如图4 所示。在FPGA 领域,这种定制功能是前所未有的,采用ASSP 进行设计是无法实现的。 图4. Altera 视频工作台支持不同层面的定制功能 采用Altera 视频工作台开发设计时,可以使用两种创新技术实时进行更新: ■ 数据包格式流接口——设计用于在功能模块之间同时传送视频和控制数据包。 ■ 算法功能模块配置——可以配置为存储器映射组件,通过写入相应的控制寄存器,实时更新功能。 Avalon-ST 视频协议是Altera 新的低开销流协议,提供面向数据包的方法来发送视频和控制数据。控制数据包用于发送动态参数,该参数描述流视频帧格式。这些参数应用于将要到达的下一视频数据包,或者在编译时设定,用在复位后接收到的第一个视频数据包上。( 表2 列出了控制数据包是怎样提供下一帧信息的)。数据到达时,视频数据流中的嵌入式控制数据包支持采用新数据对视频处理流水线进行重新配置。 表2. 控制数据包支持对视频流格式的动态更新 除了通过流接口实现运行时更新, Altera 开发的大部分视频功能模块都具有运行时更新功能。这表明,这些模块使用存储器映射从机接口,支持对状态机和片内处理器的更新。每个从机接口支持对一组控制寄存器的访问。例如,可以使用片内处理器,在运行时更新这些控制寄存器。在新一帧的开始,更新后的控制数据被装入到IP 功能模块中。这样,您可以在系统运行时更新图像大小和缩放系数,改变缩放比。图5 显示了Altera 视频工作台多相缩放引擎是怎样实现运行时控制的。 图5. 更新缩放功能 为进一步定制设计,您可以针对MegaCore 功能来修改参数。Altera 开发的所有视频功能都是可以进行参数赋值的。如图6 所示,利用去隔行器功能,您不但可以选择去隔行算法,还可以选择默认场、直通模式、外部存储器缓冲帧数量、输出帧速率和运动控制补偿等算法。 图6. 参数赋值硬件功能模块 Avalon-ST 和Avalon-MM 接口标准的开放即插即用规范意味着您可以先进行图像格式转换设计,然后,采用定制模块来替换Altera 模块。很多设计人员都有适合自己应用的定制算法。为实现定制算法的简单集成,Altera 提供支持Avalon-ST 接口打包器的HDL 模板。打包器包括以下模块: ■ VIP 控制数据包解码器——从数据流中解码VIP 控制数据包,将解码后的数据( 宽度、高度、隔行信息)作为单独的信号发送给算法功能模块。 ■ VIP 控制数据包编码器——根据接收到的宽度、高度和隔行信息对VIP 控制数据包编码,将其插入到数据流中。 ■ VIP 流控制打包器——围绕用户算法进行打包处理,实现 Avalon-ST 与简单读写接口的流控制转换。 ■ 用户算法内核——HDL 模板在用户算法模块中提供了简单的设计实例。您可以采用自己的算法替代这一模块。 图7 所示为HDL 模板的高级结构视图。 图7. Avalon 流HDL 模板 Algolith 作为Altera IP 合作伙伴,是视频IP 领域的专业公司,采用了HDL 模板来评估其内核。Algolith 开始时采用Altera 参考设计进行图像格式转换,然后使用自己的专用运动自适应去隔行器替代Altera 去隔行器,并提供给用户,在硬件中进行评估。同样, Algolith 使用Altera 视频设计工作台开发了参考设计,帮助用户评估他们的噪声抑制IP。 4 结论 Altera 视频工作台为广播基础实施系统实现图像格式转换提供所有必须的关键功能。采用Altera 视频设计工作台和图像格式转换参考设计, FPGA 设计人员现在可以使用以前只有广播ASSP 才能提供的功能,而且还具有灵活性和硬件定制等优势。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)