FPGA实现32阶FIR数字滤波器的硬件电路方案

时间:08-27

来源:互联网

点击:

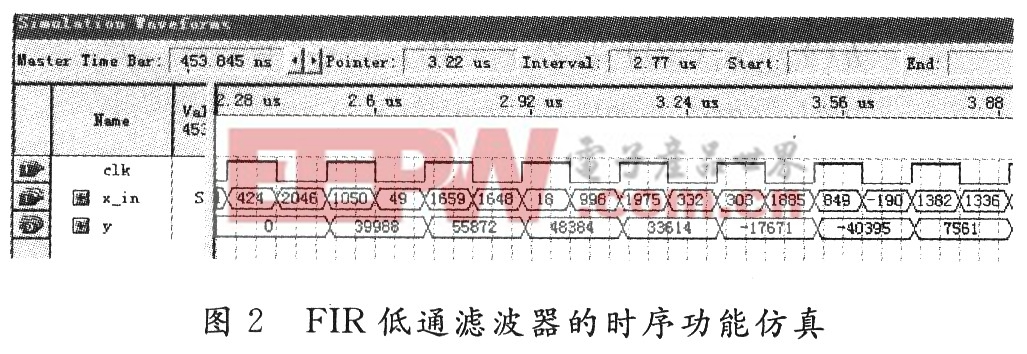

号,y为滤波器输出信号。图2并不能很直观地看出并行分布式算法产生的滤波效果,可以将QuartusⅡ中。vwf文件转化为。tbl文件,在Matlab中按照一定形式编程可以得到时域及频域波形图,如图3,图4所示。

图3,图4中,软件仿真是直接在Matlab中用输入信号与滤波系数卷积得到的,在时域波形中软件仿真输出信号与理想信号相比有一定时间延迟,而QuartusⅡ仿真与软件仿真结果中幅度的差别是由于硬件输入量化产生的。

从时域或者频域波形图可以看出,频率为30 MHz的信号被滤除掉,只有频率为1 MHz的信号通过滤波器,达到了滤波的目的。

4 结 语

本设计选用Stratix系列芯片,最大处理速度可以达到200 MHz以上。本文没有考虑线性相位的滤波器对称性,在考虑线性相位的基础之上结合一些其他算法可以降低器件数量和进一步提高处理速度。由于FPGA器件的可编程特性,在本设计中可以修改滤波器参数,得到高速处理的高通或者带通数字滤波器,具有一定实用价值。另外,本文利用QuartusⅡ与Matlab联合仿真,极大地提高了FPGA的设计效率。

- 用CPLD实现FIR数字滤波器的设计(08-07)

- 用8位微处理器实现数字低通滤波器设计(05-15)

- 基于LabVIEW的DSP设计(04-10)

- DSP滤波器用于扩展数字化仪器的性能(01-25)

- 基于DSP的并联电力有源滤波器的仿真研究(02-08)

- 基于DSP的滞环跟踪型有源电力滤波器数字控制系统(02-21)