嵌入式UART接口模块的设计

数。

UART内核在计数器到达计数上阈后便进入发送完成模式,并且输出发送完成信号。

3 UART顶层模块的仿真测试

将上述各个模块的VHDL代码生成原理图符号,并在原理图编辑工具中将各个模块连接起组成1个完整的UART模块。为了验证UART模块的正确性,对UART的发送过程和接收过程分别进行了波形仿真。

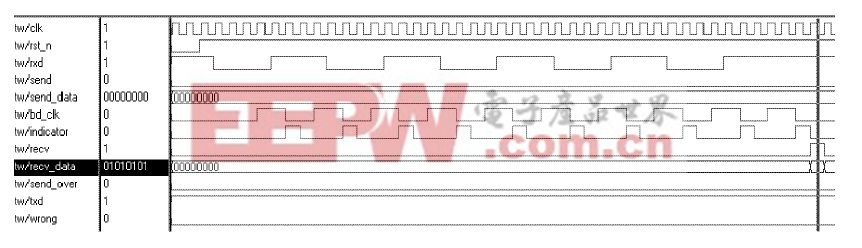

为便于观察波形,波特率产生器设置为4个系统时钟产生一个完整的波特率时钟。图9是UART模块接收过程的仿真波形图。

图9 UART数据接收过程的仿真波形图

由仿真波形图可以看出,接收端RxD上的数据序列为0101010101,起始位‘0’后为数据位“10101010”,最后一位为停止位‘1’。在10个波特率时钟之后,UART发出1个接收完成信号recv=‘1’,并在数据输出端“new_data”将接收的数据输出给后续数据处理模块。由于发送数据时首先发送数据的最低位,因此接收的数据应为“01010101”,将光条放置数据输出端“new_data”的数据输出波形上,可以从数据栏看到此时数据输出端new_data=“01010101”,UART数据接收功能完全正确。

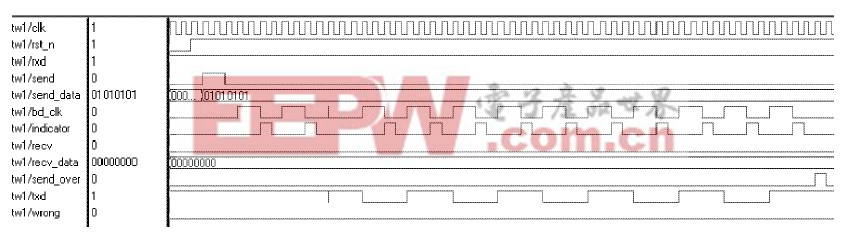

图10为UART发送过程仿真波形。由图可以看出,send=‘1’后待发送数据为“01010101”,将待发送数据加上起始位和停止位,并从最低位开始发送,则发送端txd上的数据序列为“0101010101”,发送停止位后,发送结束信号send_over=‘1’。图10证明UART数据发送功能完全正确。

图10 UART数据发送过程的仿真波形图

4 结语

介绍了UART在可编程逻辑器件FPGA上的实现,并通过实际电路验证了设计的功能,使用FPGA不仅可以方便地用串口协议与PC机进行串行通信,而且扩展了板级系统的接口功能。应用在可编程器件FP2GA内部,可以很大程度地减少电路板的使用面积,并提高系统的稳定性和可编程性。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)