嵌入式UART接口模块的设计

程是数据接收和数据发送。

由于这两个过程中移位寄存器工作在波特率时钟下,所以计数器模块的时钟就是与波特率时钟同步的波特率发生器提示信号indicator,这样每输出1个完整的波特率时钟周期计数器就能增加1。

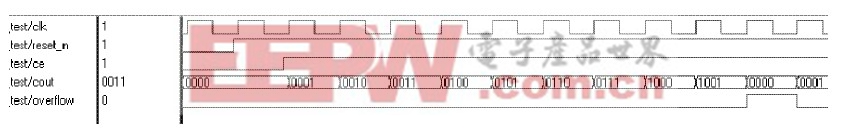

计数器的仿真波形图如图6所示。

图6 计数器仿真波形图

计数器在复位后并且ce有效时开始计数,并且在第10个时钟周期输出提示信号overflow。

2.5 发送数据缓冲器模块

发送数据缓冲器模块的功能是将要发送的并行数据转换成串行数据,并且在输出的串行数据流中加人起始位和停止位。缓冲器首先将要发送的8位数据寄存,并在最低位后添加起始位‘0’,在最高位前添加停止位‘1’,组成10位要发送的数据,然后根据UART内核模块的计数值将相应的数据送入移位寄存器输入端。

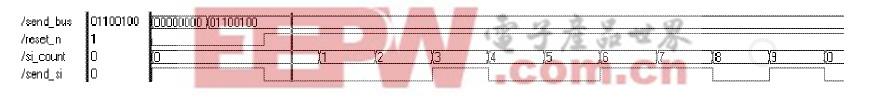

UART内核模块输出的计数值是从0依次计到9,即先将要发送数据的最低位送入移位寄存器。发送数据缓冲器的仿真波形图如图7所示。

图7 发送数据缓冲器仿真波形图

由波形图可知,发送数据缓冲器在复位后,在输入的计数值si_count为0时,send_si输出起始位‘0’。在输入的计数值si_count为1~8时,send_si分别输出send_bus上相应的数据位。在输入的计数值si_count为9时,send_si输出停止位‘1’。

2.6 UART内核模块

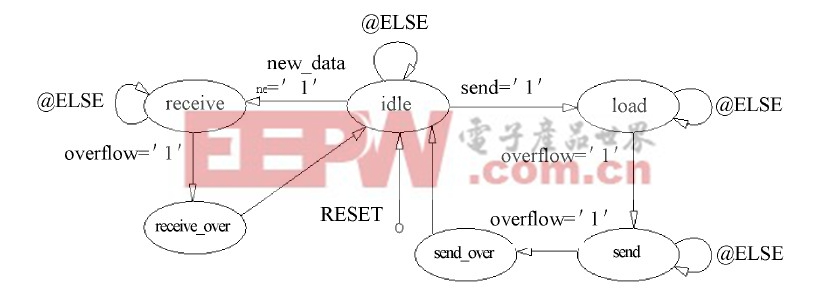

UART内核模块是整个设计的核心。在数据接收时,UART内核模块负责控制波特率发生器和移位寄存器,使得移位寄存器在波特率时钟的驱动下同步地接收并且保存RS232接收端口上的数据。在数据发送时,UART内核模块首先根据待发送数据产生完整的发送数据序列(包括起始位、数据位和停止位),之后控制移位寄存器将序列加载到移位寄存器的内部寄存器里,最后再控制波特率发生器驱动移位寄存器将数据串行输出。UART内核模块的主要功能是控制数据接收、数据加载和数据发送的过程,这可以用状态机来实现,其状态图如图8所示。

图8 UART内核状态转移图

(1)数据加载过程。数据的接收过程可以定义3个状态:空闲“idle”状态、接收“receive”和接收完成“receive_over”。UART内核模块在复位后进入空闲状态。如果信号检测器检测到数据传输,即new_data=‘1’,UART内核检测到此信号就会进入接收状态。

在UART进入由空闲状态转为接收状态过程中,需要进行一系列的接收预备操作,包括将子模块复位、选择移位寄存器串行输入数据以及选择移位寄存器的输入时钟等。进入接收状态后,波特率发生器开始工作,其输出波特率时钟驱动移位寄存器同步的存储RS232接收端口上的数据,并且其提示信号“indicator”驱动计数器进行计数。当所有数据接收完成,计数器也达到了其计数的上阈,此时overflow=‘1’,通知UART内核进入接收状态。UART内核进入接收完成状态的同时,会检奇偶校验的结果,同时使得子模块使能信号无效,以停止各个子模块。

UART内核的接收完成状态仅保持1个时钟周期,设置这个状态的作用是借用一个时钟周期复位信号检测器,准备接收下次数据传输。

检测器,准备接收下次数据传输。

(2)数据加载和发送过程。数据加载和发送的过程都是为发送数据而设定的,所以将它们放在一起进行介绍,可以用4个状态来实现上述的过程,即空闲、加载、发送和发送完成。其中的空闲状态是UART内核复位后的空闲状态,与上面介绍的数据接收过程的空闲状态一致。数据加载过程在数据发送过程之前进行。

UART内核复位后进入空闲状态,当探测到发送控制信号有效时,即send=‘1’,便会进入加载状态开始数据加载。在进入加载状态的同时,UART内核会将移位寄存器、计数器复位,并且通过选择信号使得移位寄存器的输入为发送数据缓冲器模块产生的串行数据序列,使得移位寄存器和计数器的工作时钟为系统时钟。

进入加载状态后,在UART内核控制下,发送数据缓冲器模块会将完整的待发送序列加载到移位寄存器的数据输入端,发送的序列是和系统时钟同步的,移位寄存器在系统时钟的驱动下不断读入输入端数据并保存在内部寄存器内。在移位寄存器加载数据的同时,计数器也在时钟的驱动下进行计数,由于都是工作在系统时钟下,所以当所有数据被加载时,计数器也达到了计数的上阈(即串行数据的总量),此时overflow=‘1’,通知UART内核进入发送状态。UART内核进入发送状态的同时会改变几个选择信号,比如将移位寄存器的时钟设为波特率时钟,将计数器时钟设为波特率的提示信号,最重要的是将输出信号送到RS232的发送端口TxD上。发送的过程和接收类似,移位寄存器在波特率时钟的驱动下内部寄存器的数据串行的发送出去,同时计数器在波特率发生器的提示信号驱动下进行计

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)