嵌入式UART接口模块的设计

在计算机的数据通信中,外设一般不能与计算机直接相连,它们之间的信息交换主要存在以下问题:

(1)速度不匹配。外设的工作速度和计算机的工作速度不一样,而且外设之间的工作速度差异也比较大。

(2)数据格式不匹配。不同的外设在进行信息存储和处理时的数据格式可能不同,例如最基本的数据格式可分为并行数据和串行数据。

(3)信息类型不匹配。不同的外设可能采用不同类型的型号,有些是模拟信号,有些是数字信号,因此采用的处理方式也不同。

为了解决外设和计算机之间的信息交换问题,即需要设计一个信息交换的中间环节接口。UART控制器是最常用的接口。

通用异步收发器(UniversalAsynchrONousReceiv2er/Transmitter,UART)是辅助计算机与串行设备之间的通信,作为RS232通信接口的一个重要的部分,目前大部分的处理器都集成了UART。

1 UART的数据格式

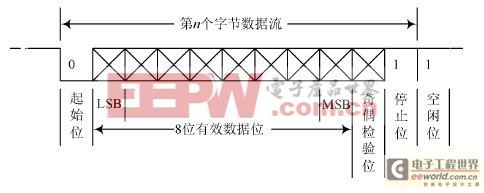

UART的数据传输格式如图1所示。

图1 UART的数据传输格式

由于数字图像亚像素在计算机中是用8位二进制表示,因此UART传输的有效数据位为8位。传输线在空闲时为高电平,因此有效数据流的开始位设为0。

接着传输8位有效数据位,先从最低位开始传送。奇偶检验位可以设置为奇检验、偶校验或者不设置校验位,由于本系统使用的传输速率不高,为了加快开发进程,减少电路面积,因此没有设计奇偶检验模块,数据流中不设奇偶检验位。最后停止位为高电平。

2 UART的基本结构

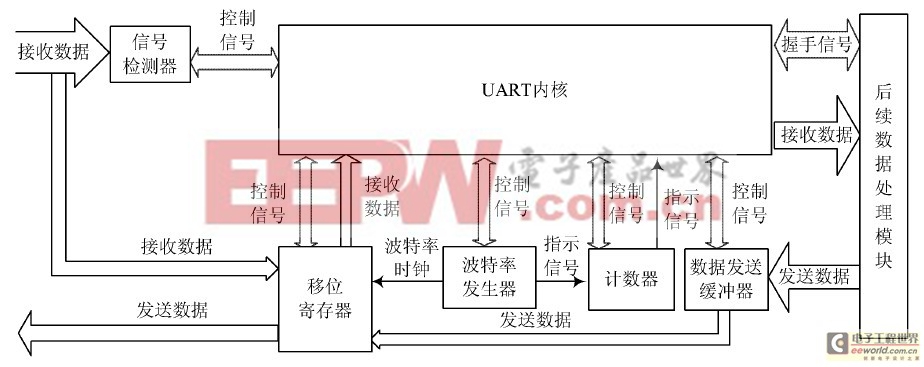

设计的UART主要由UART内核、信号检测器、移位寄存器、波特率发生器和计数器组成,如图2所示。

图2 UART基本结构

UART各个功能模块的功能如下文所述。

2.1 信号检测器模块

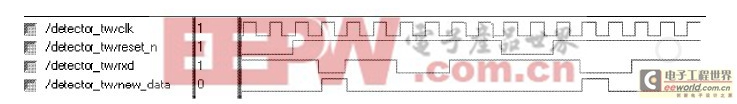

信号检测器用于对RS232的输入信号进行实时监测,一旦发现新的数据则立即通知UART内核。信号检测器的仿真波形如图3所示。

图3 信号检测器仿真波形图

其中,RxD第一次为低时,new_data信号阐述输出,之后RxD又变低,但由于信号检测器处于锁定状态,所以new_data信号并没有输出;最后,reset_n信号将信号检测器复位,RxD再次变低时,new_data又有输出。可见信号检测器的实现完全正确,其功能完全符合设计要求。

2.2 移位寄存器模块

移位寄存器模块的作用是存储输入或者输出数据。

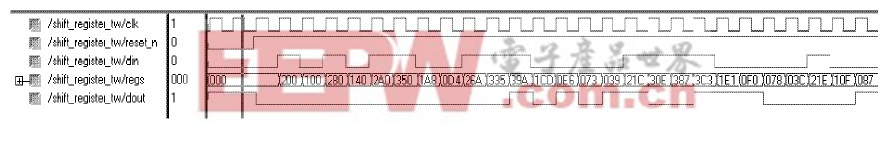

当UART接收RS232输入时,移位寄存器在波特率模式下采集RS232输入信号,且保存结果;当进行RS232输出时,UART内核首先将数据加载到移位寄存器内,再使移位寄存器在波特率模式下将数据输出到RS232输出端口上。移位寄存器的仿真波形图如图4所示。

图4 移位寄存器仿真波形图

如图4所示,移位寄存器在复位后的每个时钟的上升沿工作。由于数据发送时是先发送有效数据的最低位,因此移位寄存器是将接收的数据由高位向低位移动,dout输出移位寄存器的最低位。图中的regs数据用16进制表示。

2.3 波特率发生器模块

波特率发生器的功能是产生和RS232通信所采用的波特率同步的时钟,这样才能方便地按照RS232串行通信的时序要求进行数据接收或者发送。比如,波特率为9600b/s,即每秒传输9600b数据,则同步的波特率时钟频率为9600Hz,周期为1/9600=0.10417。

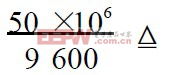

设计波特率时钟的基本思路就是设计一个计数器,该计数器工作在速度很高的系统时钟下,当计数器计数到某数值时将输出置高,再计数到一定的数值后再将输出置低,如此反复便能够得到所需的波特率时钟。该系统所用的FPGA系统时钟为50MHz,RS232通信的波特率为9600b/s,则波特率时钟的每个周期相当于

5208个系统时钟周期。假如要得到占空比为50%的波特率时钟,只要使得计数器在计数到1604时将输出置高,之后在计数到5208时将输出置低并且重新计数,就能实现和9600波特率同步的时钟。

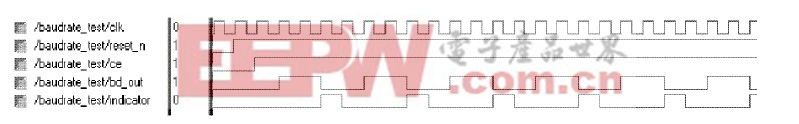

为了便于仿真,使计数器计到2时将输出置高,之后计到4时将输出置地并且重新计数。波特率发生器的仿真波形图如图5所示。

图5 波特率发生器仿真波形图

观察波形可以看到波特率发生器每经过4个时钟周期输出1个完整的波特率时钟周期,占空比为1/2,并且在每次输出波特率时钟周期之后输出1个系统时钟脉宽的提示信号indicator,UART通过此信号来了解波特率发生器已输出的波特率时钟周期个数。由波形图可见波特率发生器的工作完全满足设计的要求。

2.4 计数器模块

计数器模块的功能是可控的,在输入时钟的驱动下进行计数,当达到计数上阈时给UART内核一个提示信号。在不同的工作状态下,计数器模块的输入时钟是不同的。UART在数据发送之前需要进行数据加载(即将串行序列保存在移位寄存器内),在此工程中计数器模块的输入时钟为系统时钟,因为此时移位寄存器也工作在系统时钟下。除了数据加载,另外2个需要计数器模块的过

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)