NXP2214实现多路韦根信号采集硬件设计

韦根传感器是一种当交变磁场经过时产生输出电压脉冲的传感器。脉冲的幅度是由激励磁场的场强决定的。因此,韦根传感器不需要外界电源供电。韦根传感器的工作频率从0速率到20KHZ,脉冲的极性由激励磁场的极性所决定。由于韦根传感器非常容易和数字系统相匹配,并且系统没有可动的部件或半导体器件,这使得它们能适用于恶劣的环境和长期无人监控的场所。

1 韦根信号简介

韦根信号是两根数据线传输二进制数据,在空闲时端,两线的对0V的电源都为TTL电平的水平,也就是5V,一般通过5K电阻上拉,当有数据传输时,两根线交替地发送400uS低脉冲,当Data0线发脉冲时,数据是0;当Data1发脉冲时,发送的数据是1,不能两根线同时发脉冲。脉冲的间隔时间是1mS。在设计读卡器时,为防止使用者连接错线,造成数据口损坏,在电路设计上一定要给数据输出上加驱动级并加电阻限流。

2 接口硬件构成

接收韦根信号的上层控制设备通常是一个单片机控制系统,承担了I/O口驱动、以太网通信、数据处理、液晶显示等任务。韦根信号脉冲宽度仅为40~100μs,如果采用扫描I/O口的方式,只有满足扫描周期40 μs的条件(即采样频率高于25 kHz),才能够捕获一个信息帧内所有的下降脉冲信号,否则将因出现“脉冲遗漏”造成读数错误。如此高的扫描速度将极大地消耗CPU资源,阻塞单片机系统其他任务的正常执行,每个韦根接头都连接到CPU的一个中断信号引脚上,以中断触发的方式处理。由于CPU外部中断数量的限制,CPU包括运算逻辑部件、寄存器部件和控制部件。CPU从存储器或高速缓冲存储器中取出指令,放入指令寄存器,并对指令译码。它把指令分解成一系列的微操作,然后发出各种控制命令,执行微操作系列,从而完成一条指令的执行。指令是计算机规定执行操作的类型和操作数的基本命令。指令是由一个字节或者多个字节组成,其中包括操作码字段、一个或多个有关操作数地址的字段以及一些表征机器状态的状态字和特征码。有的指令中也直接包含操作数本身。

为了能够接收多路信号,可以由另一个独立的单片机构成一个从机系统,以循环扫描数据总线的方式工作,专门负责多路信号的采集与处理,并将处理后的ID信息通过串行或并行方式发给主控单片机。但是这种方式增加了系统的复杂度,从而给可靠性带来隐患,同时也增加了成本。

本设计中主控制器是NXP2214,采用中断触发综合扫描I/O的新方法,只用一个CPU的中断信号,实现多路韦根接口信号的采集。韦根接口硬件电路如图2所示。韦根接口是5 V的电平,而ARM内核的CPU是3.3 V的电平,因此韦根信号首先通过芯片SN74LVC4245转换成3.3 V电平。然后,输入到NXP2214的P0.8~P0.15引脚上,这些引脚通过I/O方式扫描信号。

当有任何一路韦根接口产生低电平时,经过SN74-HC30D都会产生中断;微控制器立刻响应中断,扫描输入信号获取完整的信号帧后退出中断。这样,只需要一个中断信号,只在有信号时扫描I/O,不但不会阻塞系统其他任务的正常执行,而且可以扩展出更多的韦根接口。

3 接口软件设计

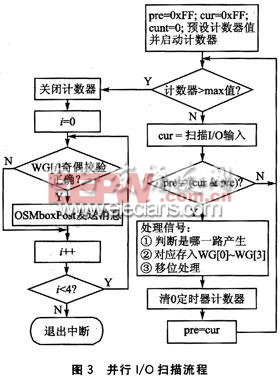

为了快速响应,使用最高级的中断优先级,当外部4路韦根接口有任何一路信号产生有效电平时,NXP2214都可以产生中断。在中断处理程序中,并行扫描4路韦根接口,并分别保存到变量。如果大于脉冲周期的时间间隔内(如2.5 ms),都没有发现任何一路信号产生有效电平,则认为传输完毕。接着处理数据和发送消息通知其他任务,然后退出中断。并行I/O扫描的流程如图3所示。

具体的扫描判断过程如下:在定时器没有超时时,首先读入韦根信号引脚的电平到cur变量;接着判断pre是否等于(curpre),即判断是否产生1到0变化的有效电平,通过下降沿判断的方式,防止误把1次0当成多个0读入。如果产生了下降沿,则判断信号是哪路韦根信号,对应存入变量WG[0]~wG。如果是DATA0产生,则直接把变量左移1位;如果是DATA1产生,则变量加1后再左移。

该并行扫描处理的方法,能够保证韦根接口在同时有多路信号产生的情况下,也可以正确操作。中断触发扫描过程,一个扫描结束后信号都保存到WG[0]~WG[3]中。

本文采用的是标准韦根输出,信号帧由26位二进制数组成,帧格式如下:

奇偶校验判断正确后,将变量中的数据去除校验位变成有效数据;然后调用OSMboxPost函数发送消息,以通知其他任务处理。

4 结 论

本文的程序和硬件均在实际产品中调试通过。实验表明,在8个通道同时完成输入连续的韦根信号的情况下,微控制器NXP2214不仅能够全部正确接收读卡器的韦根数据,还能同时完成处理TCP/IP、液晶显示以及其他任

硬件 设计 采集 信号 实现 路韦根 NXP2214 相关文章:

- 基于算法的DSP硬件结构分析(04-02)

- 电力电子装置控制系统的DSP设计方案(04-08)

- LPC2292的μC/OS-II硬件抽象层构建(04-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 基于DSP和IPM的变频调速系统的硬件设计(11-25)