基于DM365的嵌入式视频采集与传输系统

引言

德州仪器 (TI)推出的基于达芬奇技术的新型TMS320DM365 数字媒体处理器,DM365 高度集成了众多组件,其中包括符合生产要求的H.264、MPEG-4、MPEG-2、MJPEG 与VC1 编解码器,可满足智能视频处理功能的集成影像信号处理(ISP)解决方案,以及一系列板载外设等,可使开发人员将系统成本降低25%。本文围绕DM365 数字媒体处理器,对基于DM365 的嵌入式视频采集与传输系统的设计做了具体介绍。

1 嵌入式视频采集与传输系统的整体结构

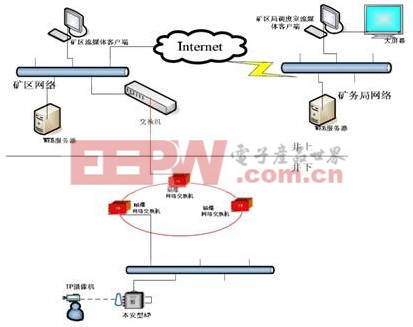

本系统利用目前先进的WiFi 无线通信技术,结合H.264 视频压缩算法构建无线视频监控系统。系统工作过程为:视频采集节点将采集到的视频、音频数据,经过前端压缩等处理之后,转换成统一的IP 数据包格式,以WiFi 无线方式发送到AP,AP 接入工业光纤以太网,实现无线与现有通信网络的无缝连接,构成感知矿山多媒体数字网络。该无线视频监控系统既可应用于矿井救灾应急通信系统,也可用于井下皮带、液压支架等煤矿安全生产管理,可极大提高矿井安全监控系统的能效,节约矿井生产成本。无线视频监控系统图如图1 所示。

图1 系统整体架构

2 系统硬件实现

2.1 系统核心架构

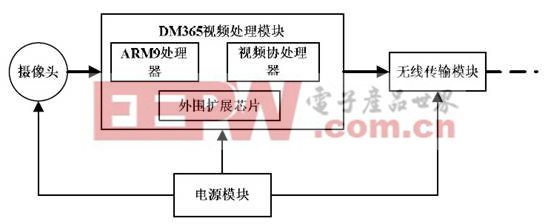

本视频采集与传输系统完成的主要功能是在煤矿井下能够进行实时流畅的多媒体通信。

系统设计的总指导原则是:在保持实时的多媒体通信质量的前提下,低功耗,低成本。节点硬件主要包括:视频采集前端、视频处理模块、无线发射模块和电源模块以及一些外围电路。

系统的原理框图如图2 所示。

图2 摄像机原理框图

2.2 视频处理模块

视频处理模块采用TI的达芬奇高性能多媒体处理器TMS320DM365 完成设备管理、音视频的压缩处理及传输通信,通过外接的以太网物理层芯片实现有线网络接口,利用转WIFI芯片GS1010 实现无线网络通信,支持TCP/IP 网络协议。

TMS320DM365 是德州仪器(TI)推出的基于达芬奇技术(DaVinciTM technology),面向便携高清视频应用的新型数字媒体处理器。该处理器延续了达芬奇家族中DM355 的处理器构架,集成了一颗ARM926EJ-S 内核,一个H.264 高清编解码协处理器HDVICP 和一个MPEG-4/JPEG高清编解码协处理器MJCP,可以支持H.264/MPEG-4 的高清视频编解码。

DM365 内部集成有视频处理子系统VPSS(Video Processing Subsystem)、H.264 协处理器(HDVICP)、ARM926EJS 的处理器以及各种相关外设,并且可以使用丰富的外设,例如高速的USB OTG 2.0。通过各种扩展的结合,DM365 可应用于相机、网络数码摄像机等领域。

2.2.1 ARM处理器

ARM 组系统采用ARMv5TEJ(32/16bit)指令集的ARM926EJ-S 内核CPU,是采用管道化流水线的32bit RSIC 处理器,工作频率为216/270/300MHz。ARM CPU 执行通常的系统控制任务,如系统初始化,配置,电源管理,用户界接口和用户命令等。ARM 作为主控和执行这些功能是因为它有一个大的程序存储空间和快速的任务切换能力,因而其更适合复杂的,多任务和通用的任务控制。

ARM 子系统(ARMSS)包含ARM926EJ-S RISC 处理器,ARM 内部存储器,嵌入式跟踪模块和嵌入式跟踪缓存模块(ETM/ETB)和系统控制外设。ARM926EJ-S RISC 处理器又包含协处理器15,内存管理单元(MMU),16KB 指令集,8KB 数据cache,写缓存和Java 加速器。ARM 内部存储器包括一个32KB 的内部RAM(32-bit 宽访问)和16KB 内部ROM。系统控制ARM中断控制器,PLL控制器,电源管理模块和系统模块。2.2.2 视频处理子系统(VPSS)

TMSDM365 拥有一个视频处理子系统(Video Processing Subsystem-VPSS)支持输入接口(Video Processing Front End-VPFE)用于外部图像外设,例如图像传感器, 视频解码器等等。

并且支持输出接口(Video Processing Back End-VPBE)用于显示设备,例如模拟SDTV/HDTV显示器,数字LCD 显示等等。

除了这些外围设备,有一个共同的缓冲存储器和DMA 控制设置,以确保有效地利用DDR2/mDDR 带宽。共享缓冲逻辑/内存是唯一的模块,无缝集成到一个图像的VPSS 内的图像/视频处理子系统。它作为主要的源和接收器给所有的VPFE 和VPBE 模块, 以从DDR2/mDDR 获得或传递数据。为了有效地利用外部DDR2/mDDR 带宽, 它通过高带宽总线(64-bit宽)DMA系统, 共享缓冲区的逻辑/内存接口。共享缓存的逻辑/内存接口通过一个128-bit 宽总线给所有VPFE 和VPBE 模块。

VPFE 模块包含图像传感器接口(ISIF), 图像通道(IPIPE), 图像通道接口(IPIPEIF)和硬件3A 统计发生器(H3A)。这些模块提供了设备强大和灵活的前端接口。

VPBE 模块包含屏幕菜单(OSD)和视频编码(VENC)模块。这些模块支持设备带有强大和灵活的后端显示接口

- 基于Linux的便携式RFID信息采集处理系统 (07-03)

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 基于DSP的图象采集与处理系统的设计(06-15)

- 基于DSP的信号采集处理系统(07-21)