基于KeyStone DSP的多核视频处理技术

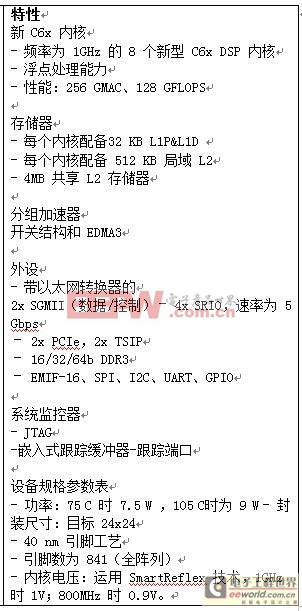

2.5 多芯片系统 实时处理超级视频 (SVGA)、4K 及更高分辨率,或处理 5 级 H.264HP可能需要不止一个芯片一起协作。要构建一个具有超高处理能力的双芯片系统,拥有可连接两个芯片的超快速总线至关重要。 第三部分描述了可满足上述所有要求及难题的 KeyStone系列 DSP架构。 3.KeyStone DSP – TI 最新多内核处理器 TI KeyStone 架构描述了广泛应用于视频处理等要求高性能和高带宽的系列多内核设备。图 2 对 KeyStone DSP进行了概括性描述。本章针对在第二部分中阐述的视频处理硬件要求对 KeyStone DSP 特性进行了介绍。 图 2 KeyStone DSP 方框图 表 1 说明 KeyStone DSP 如何满足视频处理要求。 附录A - 解码器性能相关性 编码器所采用的工具和算法以及视频内容都会影响解码器的性能。下列因素将影响解码器性能: 附录B — 运动估算和速率控制 运动估算是 H.264 编码中很大一部分内容。H.264 编码器的质量取决于运动估算算法的质量。运动估算所需的周期数取决于运动估算算法的功能特性及特征。以下是几个影响运动估算周期消耗的主要因素: 良好的运动估算算法可能消耗总编码周期的 40-50%,乃至更多。 速率控制算法是影响编码质量的主要因素。为了最大限度地提高视频的感知质量,智能速率控制算法可在宏模块和帧之间分配可用的比特。 部分系统可执行多重处理通道,以便在宏模块之间更好的分配可用比特。多条通道虽然能提高感知质量,但却要求更密集的处理。 附录C - 外部存储器带宽 由于运动估算算法的原因,编码器通常比解码器需要更高的内部带宽。编码器的要求分两种情况计算:低比特率 QCIF 和高比特率的 1080p。 两个完整的 QCIF 帧能驻留在高速缓存或 L2 乒乓缓冲器中。每个帧需要的容量不到 40 KB。采用一个参考帧对某一帧进行编码时,系统应为每次 QCIF 处理传输 80KB 的数据,并输出少量数据。200 个15 fps 的 QCIF 通道所需的总内部带宽为: 80KB * 15 (fps) * 200(通道数)+ 200(通道数)* 256/8 KB(QCIF 通道的输出比特率)= 240MB + 6.4MB = 250MB/s 假定采用最差情况中的算法来执行运动参考帧的运动估算,该参考帧可能需要从外部存储器移至内部存储器多达三次。此外,也可假定采用多达四个参考帧的高级算法。因此,单个 1080p60 通道的运动估算是: 3(复制 3 次)* 1920*1080*1(在运动估算中,每像素仅 1 个字节)*60 (fps) * 4(参考通道) = 1492.992 MBps 是否移动可进行处理和运动补偿的当前帧由以下情况来确定: 2(当前帧和运动补偿)* 1920 * 1080 * 1.5(字节/像素)* 60 = 373.248 MBps 综上所述,以上两个汇总结果规定了输出比特流。一个通道的总和为1866.24 MBps,即两个 H.264 HP 1080p60 编码器为 3732.48 MBps,这意味着约占用外部存储器原始数据带宽的 30%。

- HyperLink编程和性能考量(01-15)

- 基于KeyStone 器件建立鲁棒性系统(10-29)

- 在KeyStone 器件实现IEEE1588 时钟方案(10-15)

- 基于多核处理器的弹载嵌入式系统设计研究(02-18)

- Navigator Runtime 最大限度提高多内核效率(05-08)

- KeyStone多核SoC工具套件: 单个平台满足所有需求(09-07)