基于SoC的AC97技术硬件设计

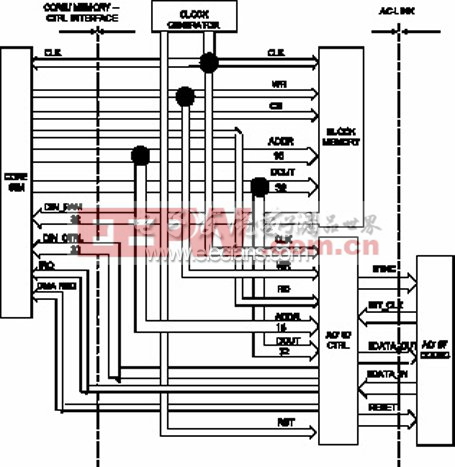

图2 SoC内核仿真环境的构成

内核模拟模块(CORE SIM)是SOC内核仿真环境的核心,以RTL代码形式下载到Vertex II FPGA中模拟DSP内核的单周期指令,可以实现读写内存、访问音频控制器(包括读写FIFO、CRBUF以及CSRS)、响应并处理中断请求或DMA请求。其中,DIN_RAM是32位内存数据输入总线;DIN_CTRL是32位音频控制器数据输入总线;DOUT是32位数据输出总线;IRQ是音频控制器中断请求;DMA REQ是音频控制器DMA请求;RST是音频控制器异步复位。

块内存模块是由Vertex II FPGA中的块内存实现的单端口内存,这种内存的时序与常规SRAM相同,可以模拟最大126KB的片上SRAM。在Xilinx集成开发环境(ISE)中调用CORE Generator,就可以生成

这种静态内存。如果运用Memory Eidtor工具生成cgf和coe文件(块内存的配置文件),就可以在为FPGA下载BIT文件的同时给块内存赋初始值。基于FPGA这项强大的功能,就可以将从个人电脑上提取出来的PCM音频码下载到块内存中,然后在内核模拟模块的控制下,通过音频控制器传送到音频编解码器中,由此实现音频播放。

时钟发生模块(CLOCK GENERATOR)可发出27MHz、54MHz以及108MHz三种时钟,并且产生音频控制器异步复位信号RST。MICroBlaze开发电路板上的晶振发出27MHz和50MHz的占空比1:1的方波信号作为时钟发生模块的输入,调用数字锁相环硬核模块(CLOCKGEN.v和CLOCKGEN.ucf)可输出各倍频时钟(本设计用108MHz)以及异步复位信号RST。AC'97 CTRL是以RTL形式下载到Vertex II FPGA中的音频控制器逻辑。AC'97 CODEC是National Semiconductor公司的LM4549 AC'97 CODEC芯片。

内核模拟模块的实现原理

RTL代码模拟的都是流水线中的指令执行级,是音频控制器和内核直接交互数据的级别。根据DSP内核在指令执行级的行为和接口特性,可以灵活地改变内核模拟模块的接口和内部信号(通过改变RTL代码),形成不同的仿真环境。测试在新的仿真环境中音频控制器与内核的工作是否协调稳定,如果结果不理想,就应更改音频控制器的设计。这样就能使音频控制器的特性也能和内核达到最好的协调。

基于SoC内核仿真环境的放音实例

下面给出基于SoC内核仿真环境播放音频的实例。音频来源于Windows2000操作系统初始安装后winnt/media目录下的Utopia Windows Start.wav(153KB,16位单声道的wave文件),提取出文件中的PCM音频码后下载到Vertex II的块内存中。音频控制器在SoC内核仿真环境中控制音频编解码器工作,连接耳机到MicroBlaze开发电路板的耳机插口,可以听到维持将近3秒钟的音频信号,和原音频文件的声音基本一致。使用音频分析软件Audicity来分析音频播放效果,原始音源与开发板播放的音频略有不同,其原因有以下3点。(1)电脑声卡录音起点和原音频的放音起点不同; (2)由于块内存的最大容量为126KB,所以所录波形文件只截取了原文件(153KB)的前2/3部分。(3)经过SoC内核仿真环境放音,并由电脑声卡录音得到的音频与原音频的幅度必然不同。第1、2两个因素引起两个波形在时间轴方向上的偏差,因素3引起幅度轴方向上的偏差。尽管存在这些差异,但完全可以说明在SoC内核仿真环境中,所设计的音频控制器逻辑功能正确,与内核能够协调工作。

总结

本文根据所设计的音频控制器的结构详细介绍了构建SOC内核仿真环境来测试音频控制器的思想和实现方法。基于这个仿真环境,不但可以测试音频控制器实际录放音的效果和性能,更重要的是可以及时反映其与内核的协调程度。这样就可避免孤立设计音频控制器而不考虑其与SoC系统协调的弊端,明显提高后期整合SoC系统的效率。

- 基于算法的DSP硬件结构分析(04-02)

- 电力电子装置控制系统的DSP设计方案(04-08)

- LPC2292的μC/OS-II硬件抽象层构建(04-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MCU+DSP的运动控制硬件平台设计(10-01)

- 基于DSP和IPM的变频调速系统的硬件设计(11-25)