采用FPGA实现 DisplayPort

不过, 对于开发这些电视或连接至这些电视的电子产品的设计工程师来说,所有这些最新特性都意味着需要非常高的带宽。例如,一部具备 800 万像素的四声道 4Kx2K 高清电视(可为家庭提供数字影院效果)需要的带宽是当前顶级电视和显示器在理想工作状态下所需带宽的四倍,这意味着在机顶盒与高清电视之间存在巨大的数据吞吐量。

这种对更高带宽的需求并不单单来自消费产品市场,为了满足 MRI 和 CT扫描、命令与控制、菊花链显示、电子公告牌与 DNA 3D渲染、航空器、天气以及人体构造等众多应用领域的显示需要,广播设备、数字显示、科研以及医疗市场也在不断加大对带宽的要求。

为了在控制成本的同时还能有助于满足这种带宽需求,视频电子标准协会 (Video Electronics Standards Association) 于 2007 年向市场推出了DisplayPort,并随后积极与合作伙伴展开合作,对 DisplayPort 进行优化。如今,VESA DisplayPort 1.1a 已能够在单根线缆内支持多达 4 个通道且每通道最高 2.7Gbps 的数据率,而 DisplayPort1.2 又将支持的数据数率翻了一番,达到5.4Gbps(足以在单显示器应用中支持3,840 x 2,400 像素 (60Hz),或 4 台显示器应用中的 1,920x1,200 像素,或 2,560x 1,600 像素的 3D 显示 (120Hz))。DisplayPort 可同时支持两种嵌入式显示,如笔记本电脑的显示器,以及视频“源端”设备(机顶盒、DVD 播放机、PC 图形卡以及笔记本电脑)和独立显示设备(HDMI 与 DisplayPort 标准文档中所称的“宿端”设备)之间的盒至盒连接 (box-to-box connection)。

图1 TED Spartan-6 FPGA 消费类视频套件

一些芯片制造商已针对上述应用推出了现成的标准发送器和接收机,而赛灵思推出了名为 Xilinx LogiCORETM DisplayPort v1.1(v1.2 将在 IDS 12.1中配套提供) 的灵活可编程 VESA DisplayPort v.1.1a 解决方案。该 IP 可随时提供给赛灵思的客户,但在用户展开设计之前,建议先了解与该标准的部分关键功能有关的其它背景信息,如Policy Maker,以及如何使用我们即将推出的 XAPP“使用 MicroBlazeTM 嵌入式系统实施 DisplayPort Source PolicyMaker 控制系统参考设计”在东京电子设备 (TED) 提供的 Spartan-6 消费类视频套件上完成实施工作。

Policy Maker — 关键性差异

对于显示市场来说,DisplayPort协议标志着连接技术的重大变革。这次转型的意义不亚于在 Intel 主导的 PC 市场上从并行 PCI 总线升级至串行 PCI Express。在显示市场上,VESA 通过DisplayPort 引领着从 VGA、DVI 以及HDMI 等协议成功升级至高速串行收发器、基于包的层架构协议。与并行协议不同,串行分组协议在实现和维持连接或链路方面要多一层复杂性。在 VESA DisplayPort 1.1a 规范中,控制功能被划分为 Link Policy Maker 和 Stream Policy Maker。Link Policy Maker 可管理链路,并负责保持链路同步。其任务包括发现链路、对链路进行初始化和维护。Stream Policy Maker 可管理传输初始化,并通过底层硬件对行动序列施加控制来维护同步流。

Policy Maker 的上述要素需根据特定的实施来决定,而且可在操作系统、软件驱动程序、固件或者 FPGA 逻辑中进行配置。为简化使用,许多商用DisplayPort IC 将 Link 和 Stream PolicyMaker 对设计人员隐藏。如果用户的显示要求恰与套装的 DisplayPort ASSP相匹配,则其价格和易用性确实无可争辩。但是,想要让产品在竞争中脱颖而出的设计人员则倾向于采用 FPGA。

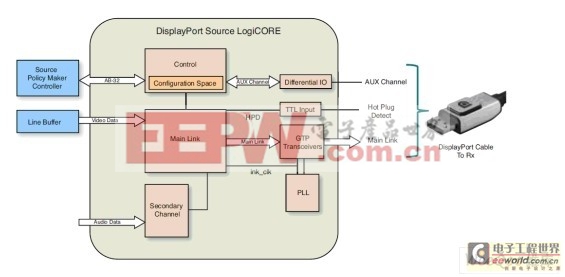

图2 DisplayPort Source Policy Maker Controller System Reference Design 与 LogiCORE 源端高层结构图

Source Policy Maker参考设计

DisplayPort Source Policy Maker控制系统参考设计采用MicroBlaze嵌入式系统来实施与商用套装 DisplayPort 芯片类似的功能,且具备可进行源代码定制的额外优势。通过使用 Source Policy Maker Controller System Reference Design 的应用手册,用户不必对 Policy Maker 进行详细了解即可顺利启动设计工作,仅需简单地

FPGA IP 嵌入式 PLD CPLD SoC 数字信号处理 消费电子 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)