基于FPGA 的ATM SAR 及其接口设计与实现

元头的PT 域指示数据的开始、中间和结束,将接收 到的信元还原成完整的一个CPCS-PDU 包存入FPGA 存储器后发送给CS 子层。

2.2 发送流程模块设计

根据数据发送的流程来划分功能模块,分为 CS 子层数据的存储模块、ATM SAR 模块 和UTOPIA 接口发送模块三个主要功能模块。

CPCS-PDU 存储模块:实现:CPCS-PDU 存储模块输入数据宽度为16 位,输出数据宽度 为8 位,有可读/写、片选信号和地址总线。上层先查询RAM 的可写(WR)信号有效时, 将CPCS-PDU 包发送到16 位数据总线上,一个包发完后置RAM 的片选(CS)信号为无效; RAM 将数据线上的数据顺序存入,并对PDU 包的字节数计数,用RAM 的头两个字节存放 包的长度,3~6 字节存入VPI/VCI 值。一个PDU 包存入后置可写(WR)信号无效,置可 读(RD)信号有效。

SAR 拆分和ATM 模块实现:首先在ATM 层创建一发送FIFO,用来存放ATM 层生成的 信元。在发送双口RAM 可读的状态下,从CPCS-PDU 存储器读出头2 个字节(即数据包的 长度)与48 比较,大于48,生成中间信元;等于48 生成末尾信元,存入FIFO,准备发送。

UTOPIA 发送模块实现:UTOPIA 接口实现采用信元级握手传输方式,它是以信元为单 位进行传输,传输中的控制信号是以信元为基础的。设计一个发送控制模块,通过地址信号 轮询PHY 层状态,接收来自ATM 层的UTOPIA 控制信号、物理层的控制信号以及发送FIFO 的状态信号,控制信元一个一个地从ATM 层发送到物理层,时序要求满足ATM 论坛关于 UTOPIA 接口Level1 和Level2 标准。

2.3 接收模块流程设计

根据数据接收的流程来划分功能模块,分为UTOPIA 接口接收模块、ATM SAR 组装模 块和接收SAR-PDU 存储模块三个主要功能模块。

UTOPIA 接收模块模块实现:首先在ATM 层创建一个接收FIFO,再设计一个接收控制 模块,通过地址信号轮询PHY 层状态,接收来自ATM 层的UTOPIA 控制信号、物理层的 控制信号以及接收FIFO 的状态信号,控制信元一个一个地从物理层传送到ATM的FIFO 中。

ATM和SAR 组装模块实现:在SAR-PDU存储器可写的状态下,不断读入信元接收FIFO 的53 字节数据,剥去信元头还原为SAR-PDU,由信元标识PT 来判断SAR-PDU 是中间还 是末尾数据包,并计算CPCS-PDU 包长度,最后在SAR-PDU 存储器中存入一个完整的 CPCS-PDU 包,包的长度存入存储器的头两个字节中。

接收 SAR-PDU 存储模块实现:接收SAR-PDU 存储模块输入数据宽度为8 位,输出数据 宽度为16 位,有可读/写、片选信号和地址总线,如图4-8。可写(WR)信号有效时,RAM从第六个字节开始顺序存入SAR-PDU(头2 个字节放包长,后4 个字节存放VPI/VCI 值), 直到存入最后一个SAR-PDU,RAM 头两个字节存入CPCS-PDU 包的长度,置可写(WR) 信号无效,置可读(RD)信号有效,此时一个完整的CPCS-PDU 包已经存好,供CS 子层 读取。

3 软、硬件调试

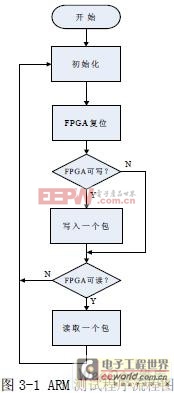

编写基于ARM7处理器μcLinux 系统下的CPCS-PDU 数据包的收发程序,在Red Hat9.0 系统中(ARM 工具链已建立好)编译通过后,下载到在ECPB 板上运行。程序主要完成ARM 处理器对外设FPGA 的复位、读、写等操作,流程图如图3-1 所示。

QuartusⅡ软件的SignalTapⅡ逻辑分析仪可以用来采集FPGA 内部节点和I/O 引脚信号, 通过JTAG 端口送往逻辑分析仪显示。调试过程中主要利用SignalTapⅡ逻辑分析仪和示波 器,通过收、发数据包来验证FPGA 中数据处理的正确性。

调试步骤如下:

(1)ARM 测试程序和FPGA 程序下载;

(2)ECPB 板ARM 初始化配置、CMTC 板UTOPIA 接口初始化等;

(3)程序运行; 按照上述步骤验证 FPGA 芯片设计是否满足任务需求。经过发送和接受数据包测试后得 出,经反复数据测试比对,FPGA 工作正常,满足任务要求。

4 结束语

本文的创新点在于对 ATM 技术和UTOPIA 接口时序进行了深入、系统的分析与研究, 以替代现有专用通信处理器为目标,提出了一种采用FPGA 来实现ATM SAR 和UTOPIA 接 口的解决方法。设计好的FPGA 芯片与上层ARM 处理器和物理层CMTC 板对接后应用于 ADSL 测试系统中,在数据接收和发送两个方向,FPGA 均正确完成上述功能,且工作稳定, 具备了专用通信处理器MPC866 同样的功效。作者相信,本文的研究成果,即采用FPGA 在基于ARM 处理器的环境中实现了ATM 接口,对于ATM 应用领域的成本降低和灵活性有 着较大的实际意义,也为替代专用通信芯片迈出了成功的一步。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)