新型数据格式转换的FPGA实现

frac_28(0)的权值是2-28。此进程由frac_part发生变化来启动,完成转换的时间是瞬时,也可以认为是一个时钟周期。

3 仿真结果及分析

首先用ModelSim进行功能仿真,其结果如图3所示。输入的实数为125.763,输出结果经Matlab逆向求值同输入值进行比较,验证了转换结果的正确性。一个数的正确转换并不能说明问题,下面将验证此转换方法的可行性。

选取具有代表性的实数对转换方法的性能进行验证。主要验证两个方面:

(1)是否在预定域内具有全覆盖性;

(2)是否能对此域中的最小值进行有效表示。

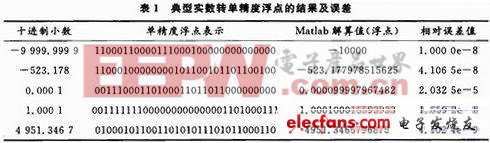

结果如表1所示。

根据转换原理,最小值所转换的误差最大,但最大值的转换误差不一定最小(因为存在舍入)。这个最大的转换误差在10-5量级,当待转换实数的绝对值大于整数1时,转换的误差将小于10-5量级,可达10-9量级。这样的转换误差可以满足大多数浮点运算环境下的精度需要。实验验证了此转换方法的有效性和“全覆盖性”。

在完成仿真测试后,将程序进行综合,布局布线,最后生成位流文件下载到FPGA芯片中进行验证。在实际的芯片中将转换结果和已仿真得到的结果进行比较,并输出指示信号。从实际的电路输出结果看,和仿真结果完全一致,证明了此方法在实际芯片中可行性。因为采用的是流水线操作,所以仿真所用的周期数和实际周期数是一致的。该实验在50 MHz的时钟下用时6个周期(即0.12μs)完成转换操作。而在最常用的串口传输波特率9 600 b/s下,传送1个码元的时间为10-1ms量级。从而可以得出:完成从ASCII码所表示的实数(-9 999.999 9~+9 999.999 9)到单精度浮点的转换所用的时间将在10-1μs量级以下,具有较高的实时性。

4 结语

本文的实现向单精度浮点的转换占用1 161个slice资源,在FPGA发展到今天,FPGA的容量和资源都有了很大提高的情况下,这样的资源占用量在大多数应用中是可以承受的。本文的设计可以很容易地根据实际实数的范围进行调整,并且可以推广到其他浮点格式,可有效地为浮点IP核提供快速且具有高精度的数据源。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)