嵌入式1394总线接口的设计和实现

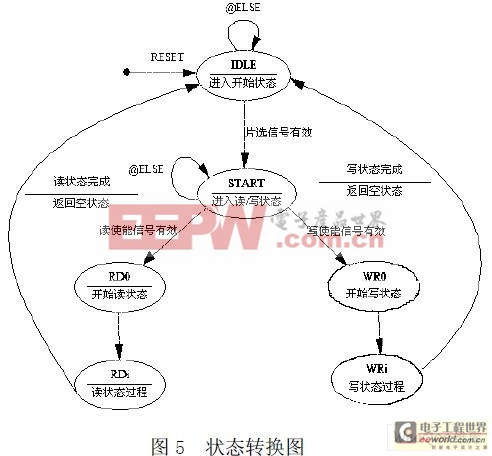

基于以上情况,本设计中使用“有限状态机”的方法实现嵌入式处理器与链路层芯片的时序匹配,保证在处理器的一次读写操作中数据能正确有效地传送。结合图2、图3 和图4的读写时序给出状态转换图如图5。此状态机一共由6 个状态组成,分别为IDLE、START、RD0、RDi、WR0、WRi。在RESET 信号有效时设计进入复位阶段,复位后状态机进入IDLE 状态;在IDLE 状态中,如果片选信号有效,状态机进入START 状态,同时输出给链路层控制器MCS 端口低信号,选通链路层芯片寄存器;状态机进入START 状态后,开始检测读写使能信号,如果读(写)信号有效,则进入RD0(WR0)状态,同时向链路层控制器芯片读(写)的地址;在RD0(WR0)状态中,检测链路层控制器芯片的MCA 管脚信号,在MCA 有效时读(写)有效数据,并向DSP 输出RDY 有效信号,状态机进入RDi(WRi)状态,经过一个时钟后释放数据和地址总线,返回IDLE 状态。

三、 设计实现

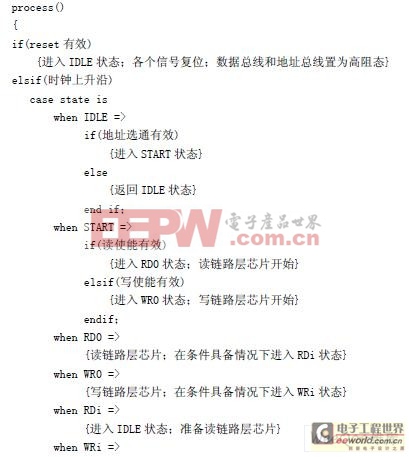

目前用于 FPGA 设计的主流硬件描述语言主要有VHDL 和verilog HDL,本设计借助VHDL语言实现。下面简要列出实现状态机的VHDL 代码结构:

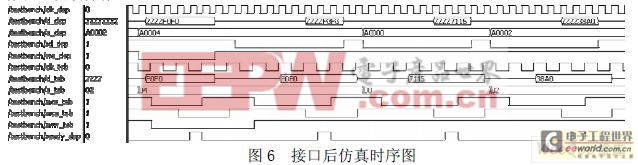

将此设计方法实现的电路下载到实际系统中进行验证,试验结果表明,该设计能成功完成TMS320V33 对TSB12LV32 芯片读写控制功能。接口后仿真时序如图6 所示,包括一次写操作和三次读操作。

四、 结论

本设计实现的 TMS320V33 与1394 总线链路层芯片TSB12LV32 的接口设计方法,设计思路清晰,时序准确,并且具有一定的灵活性和通用性,其他类似处理器与1394 总线链路层芯片的接口都可以采用类似的设计方法。

本文的设计方法为其它各种处理器与外设接口的匹配设计实现提供了有益的参考。

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)