嵌入式1394总线接口的设计和实现

一、 引言

IEEE1394 是1986 年由苹果电脑公司针对高速数据传输开发的一种总线接口,并于1995年由美国电气和电子工程师协会(IEEE)制定成标准,旨在取代并行SCSI 接口。目前为止,它主要发展为IEEE1394-1995,1394a,1394b 等系列标准。1394 作为一个工业标准的高速串行总线,已经被广泛应用于数字摄像机、数字照相机、电视机顶盒、计算机及其外围设备、DVD 设备等等,甚至在航天军事领域也有一定的应用潜力。这些设备便携性的需求加快了它们集成度的提高,这些都将使1394 总线与嵌入式处理器的结合有很广阔的应用前景。

等时传输模式的优越性使1394 总线广泛应用于图像传输领域,而数字信号处理器(DSP)在图像等信号处理方面具有很大优势,因此基于DSP 实现的1394 总线接口在图像传输和处理领域有着广泛的应用需求,但是,DSP 芯片与1394 总线芯片时序一般不能直接匹配。本文提出了一种基于DSP 的1394 总线接口实现方案,能在基于DSP 处理器的嵌入式系统上方便地实现1394 总线接口,具有较强的现实意义。

二、 设计方案

1394 总线协议包括物理层,链路层,传输层,应用层以及串行总线管理器。目前已经有很多厂家能提供1394 总线接口的协议芯片,可以很容易地实现1394 总线接口本身。本文主要介绍如何通过FPGA 实现嵌入式处理器与1394 总线链路层控制器芯片的匹配,嵌入式处理器把1394 总线设备作为外设实现数据读取和写入。整体结构框图如图1。其中DSP 是本文使用的嵌入式处理器类型,1394 链路层控制器和1394 物理层控制器是1394 总线协议芯片。FPGA 是现场可编程门阵列,是本文用于实现DSP 与1394 链路层控制器匹配的主要芯片,与分立器件相比,它具有可擦除、功耗小、体积小和调试方便等优势。本文选用ACTEL 公司生产的APA300 芯片来完成设计,它有30 万门阵列资源,已经远远满足本设计的需求。

2.1 TMS320V33

德州仪器(TI)在DSP 设计厂商中具有领先优势,TMS320V33 是TI 推出的TMS320 系列的第三代处理器的升级版本的32 位浮点运算数字信号处理器,也是目前国内外使用最为广泛的浮点DSP 芯片之一。它有24 位地址总线和32 位数据总线,本设计中使用高17 位地址信号作为选通信号,低7 位地址信号作为输出给链路层芯片的有效地址信号,低16 位数据总线作为有效数据信号,H1 是37.5Mhz 时钟信号。TMS320V33 读写外部寄存器时序如图2。

2.2 链路层控制器

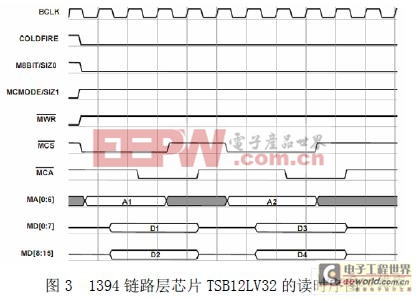

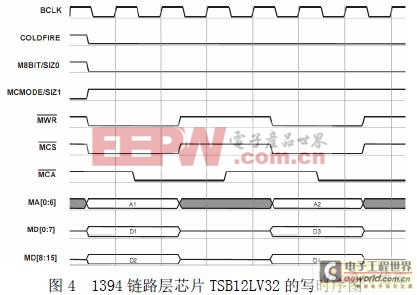

目前能提供 1394a 链路层控制器芯片的厂商有很多,芯片种类也很多。而其中TI 公司生产的TSB12LV32 功能全面,应用广泛。它是一款高性能通用1394a 链路层控制器,它主要实现1394 链路层协议。图3 和图4 是1394 链路层芯片TSB12LV32 的握手模式读写时序图。其中BCLK 代表时钟信号输入,最大工作频率是60Mhz;MWR 代表读写使能信号输入,高电平时读使能有效,低电平时写使能有效;MCS 代表选通信号输入,低电平有效;MCA 代表选通应答信号输出,低电平有效;MA 代表地址信号输入;MD 代表双向数据信号;另外COLDFIRE,M8BIT/SIZ0,MCMODE/SIZ1 为设置工作模式专用信号。在本设计中我们选用握手工作模式。

2.3 方案选择

链路层控制器最高仅 60Mhz 的理论工作频率使得高性能的TMS320V33 必须增加自己的读写周期才能与之很好的配合,TMS320V33 的读写周期可以通过RDY 信号或者增加可编程等待状态改变。在本设计中我们对TMS320V33 使用RDY 信号的方法来配合它与链路层芯片的读写时序。两种方法没有好坏之分,区别仅在于DSP 可编程等待状态的数量是有限的,但是大部分情况下增加有限的等待状态已经足够。

我们可以选择使用组合逻辑和时序逻辑来完成此FPGA 设计,虽然组合逻辑设计方法简单、占用资源少,但是它仅仅是让DSP 和链路层芯片的读写时序“凑”到一起,很难实现完全配合,而且会在读写过程中存在很多“毛刺”、“竞争”和“冒险”,不适合应用在性能要求比较高的场合。有限状态机是时序逻辑的一种,它由状态、状态转换条件和状态输出组成。它具有以下优点:1.它是同步时序电路,克服了组合逻辑顺序控制不灵活的缺点,便于与CPU 配合;2.状态机容易构成性能良好的同步时序逻辑模块,只需要将“毛刺”控制在下一个状态到来之前,这对于对付设计中的“竞争冒险”现象无疑是一个较好的办法;3.状态机的结构模式相对简单,设计方案相对固定,设计方法具有通用性。

基于以上情况,本设计中使用“有限状态机”的方法实现嵌入式处理器与链路层芯片的时序匹配,保证在处理器的一次读写操作中数据能正确有效地传送。结合图2、图3 和图

- Linux嵌入式系统开发平台选型探讨(11-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)

- 嵌入式系统实时性的问题(06-21)

- 嵌入式实时系统中的优先级反转问题(06-10)

- 嵌入式Linux系统中MMC卡驱动管理技术研究(06-10)

- FPGA的DSP性能揭秘(06-16)