IIS音频总线

IIS有4条线:串行数据输入(IISDI)、串行数据输出(IISDO)、左右通道选择(IISLRCK)和串行位时钟(IISCLK)。产 生IISLRCK和IISCLK信号的设备称为主设备。

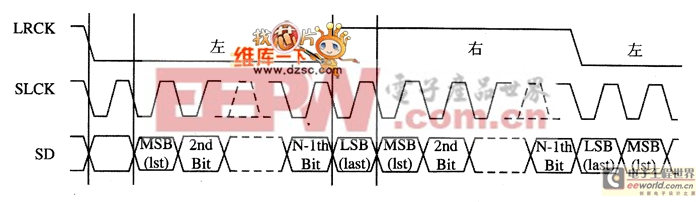

图1 IIS总线格式

串行数据以2的补码发送,首先发送高位。高位首先发送是因为发送方和接收方可以有不同的字长度。发送方知道接收方能 处理的位数是不必要的,同样,接收方也不需要知道发送方正发送多少位的数据。当系统字长度大于发送方的字长度时,字 被切断来发送。如果接收方收到比它的字长度更多的位时,多的位被忽略;若接收方接收比它字长度少的位时,不足的位被 内部设置为0。所以高位有固定的位置,而低位的位置依赖于字长度。发送器总是在IISLRCK变化的下一个时钟周期发送下一 个字的高位。

发送器的串行数据发送可以在时钟信号的上升沿或下降沿被同步。可是串行数据必须在串行时钟信号的上升沿锁存进接收 器,所以当发送数据用上升沿来同步时有一些限制。LR通道选择可以指示当前正发送的通道。IISLRCK既可以在串行时钟的 上升沿变化,也可以在下降沿变化,但不需要同步。在从模式下,这个信号在串行时钟的上升沿锁存。IISLRCK信号秽‘变 一个时钟周期之后,开始发送高位数据,这允许从发送方可以同步发送串行数据。更进一步,它允许接收方存储先前的字并 准备接收下一个字。

IIS总线模块结构框图如图2所示。

图2 IIS总线结构框图

由图2可总结出IIS总线的主要特点如下。

·双分频器(IPSR):一个用于IIS设备的主时钟发生器,另一个用于外部编解码芯片时钟发生器。

·64字节的堆栈(FIFO):发送数据时,数据被写入发送FIFO;接收数据时,数据被写入接收FIFO。

·IISCLK主时钟:在主模式下,串行位时钟由该发生器产生。

·移位寄存器:发送模式,并行数据通过该寄存器转化为并行数据;接收模式,串行数据被转化为并行数据接收。

- SPI , IIC, IIS, UART, 232,485 总结(11-28)

- 移植ucosII到STM32F103ZE(四)(11-25)

- 移植ucosII到STM32F103ZE(一)(11-25)

- 移植ucosII到STM32F103ZE(二)(11-25)

- 移植ucosII到STM32F103ZE(五)(11-25)

- 移植ucosII到STM32F103ZE(六)(11-25)