如何让7系列FPGA的功耗减半

时间:12-22

来源:电子产品世界

点击:

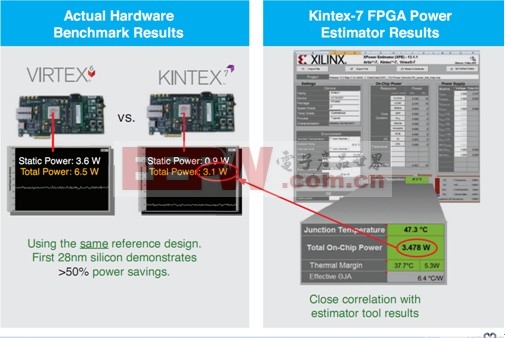

将各项标准测试结果综合在一起,证明 7 系列是用户准备用 FPGA 实现的各种应用的理想选择。客户既可以通过下列网址:http://www.xilinx.com/publications/technology/power-advantage/7-seriespower-benchmark-summary.pdf,查阅赛灵思公布的一系列标准测试结果,也可访问如下网站:http://s e m i n a r 2 . t e c h o n l i n e . c o m /registration/wcIndex.cgi?sessionID=xilinx_jun1411,观看 TechOnline 网络研讨会。 图 5:Xpower Estimator (XPE) 工具可以让设计小组更好地评估赛灵思 FPGA 的功耗特性,并与同类竞争产品进行比较 图中文字: 实际硬件标准测试结果 静态功耗:3.6W 总功耗:6.5W 静态功耗:0.9W 总功耗:3.1W 采用同样的参考设计。 首款 28nm 芯片证实可将功耗降低 50% 以上 Kintex-7 FPGA 功耗估计器估计结果 与估计器工具测得的结果紧密关联 掌握工具 最新版 XPE 功耗估计器工具(即 13.2 版)(图 5)提供了反映近期 7 系列产品变动的最新数据。该版本还提供重新架构的 GTP 和 GTH 收发器的较低功耗数据。根据普遍的需要,该版本的工具还为客户提供了必要的最高功耗数据,便于他们进行最恶劣情况下的电源和热性能设计。

- 可扩展的嵌入式网络平台(07-07)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 如何快速启动嵌入式系统开发(01-06)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 设计可靠性: MTBF—这只是开始!(09-17)

- 将SoC平台设计与DSP系统生成器相集成(07-01)