如何让7系列FPGA的功耗减半

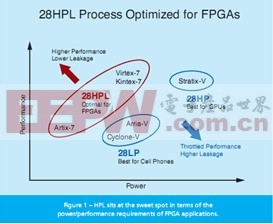

的过程中,赛灵思评估了多种 28nm 代工工艺,最终选择与台积电合作,共同开发一种专门适用于 FPGA 的工艺。这种名为高性能低功耗 (HPL) 的新工艺采用高介电层金属闸 (HKMG) 技术,可大幅地降低晶体管的漏电流并实现功耗和性能的最佳组合。赛灵思公司的产品管理总监 Dave Myron 表示,在 HPL 工艺技术问世之前,赛灵思和其他 FPGA 公司必须在给定代工厂的低功耗 (LP) 工艺和高性能 (HP) 工艺抉择。LP 工艺用于性能较低的移动应用,而 HP 工艺则是专门为高性能图形芯片和 MPU 开发的。 Myron 说:“这两种工艺对 FPGA 来说都不理想。如果选择 LP 工艺,性能就是问题,如果选择 HP 工艺,功耗就会超过预期。这两者虽然有回旋余地,但不能满足我们的需要。” Myron 继续道,FPGA 已经在大量应用中得到广泛使用,“但它们还不能完全满足图形芯片的性能要求以及商用移动电话中的 ASIC 的极低功耗要求。”Myron 说,通过共同研发 FPGA 专用工艺,台积电和赛灵思找到了兼具高速度和低漏电流的晶体管理想组合。Myron 表示(见图 1):“采用 HPL,我们能够定制工艺,使其处于 FPGA 应用的性能及功耗要求的理想平衡点上。由于我们的器件能够不偏不倚地满足性能-功耗要求,这意味着客户不必走性能或功耗的极端,从而让设计能够发挥最大的功效。” 图 1:HPL 工艺处于 FPGA 应用的性能及功耗要求的理想平衡点上 图中文字: 性能 功耗 专门针对 FPGA 优化的 28HPL 工艺 性能更高 漏电流更少 专门针对 FPGA 优化的 28HPL 工艺 Virtex-7 Kintex-7 Artix-7 Stratix-V 28HP 最适用于 GPU Arria-V Cyclone-V 28LP 最适用于移动电话 性能下降 漏电流更高 图 2:28nm HPL 工艺、28nm 高性能 (HP) 工艺和 28nm 低功耗 (LP) 工艺的性能及漏电流对比 图中文字: 漏电流 性能 GPU 的高功耗区域 增加 Vt 更高性能/功耗比 FPGA 的低功耗区域 7 系列还提供另一种称为电压 ID (VID) 的模式。客户可以通过控制 Vcc 电压和发挥部分器件的额外性能来降低功耗。每个器件都存有一个电压 ID。这个可读 VID 明确指出该器件在仍能满足性能规范条件下可运行的最低电压。 这种额外的余量令人振奋的是,为设计人员提供了更多选择。Myron 说:“客户可以选用 7 系列器件来实现他们现有的设计,同时让现有设计的功耗减半。或者他们可以保持原有的功耗水平,为系统增加更多功能,直到达到余量。这样可以降低系统总体功耗,节省板级空间,提高性能,同时大幅降低系统总成本。” 赛灵思 7 系列的所有 3 个 FPGA 产品系列和新推出的 ZynqTM-7000 可扩展处理平台均采用这种专为 FPGA 优化的 HPL 工艺。赛灵思在这些器件的所有 FPGA 结构中均采用统一的方法(即基于小型高能效模块的统一 ASMBLTM 架构)来处理。这样客户就能够在所有这些器件系列中更轻松进行设计移植:低成本低功耗 ArtixTM-7 FPGA;具有业界最佳性价比的KintexTM-7;具有业界最佳性能和最大容量的 Virtex®-7;以及集成了嵌入式 ARM 双核CortexTM-A9处理器,主要面向嵌入式应用的 Zynq-7000 可扩展处理平台。 虽然同类 FPGA 竞争产品继续采用 HP 工艺和 LP 工艺来实现单一架构的各种变体,但赛灵思坚信采用专为 FPGA 定制的工艺实现的统一芯片架构,可推动作为一种可编程平台的FPGA 技术日趋成熟,在此,FPGA 芯片仅作为平台的基础,而不是系统解决方案的全部。按照随 Virtex-6 和 Spartan®-6 FPGA 推出的赛灵思可编程平台战略,赛灵思提供的不仅是高级芯片,还包括特定市场开发板、专用开发板、IP 核、工具及技术文档,有助于客户迅速开展创新。 Myron 提到,转向使用优化的工艺和统一架构,在半导体行业中并非史无前例或者是走极端,它只是把英特尔公司率先提出的、且在过去五年得到了成功部署的一套战略用到 FPGA 上(见白皮书《在 Intel Core 微处理器架构内》)。 曾供职于英特尔公司的 Myron 表示:“2006 年,英特尔停止使用多种微处理器架构,采用单一芯片工艺实现了其功能最为强大的统一硬件架构 — Intel Core 微处理器架构,并将其应用于从高端计算服务器到移动笔记本产品等多个产品线。为什么像英特尔这样看似有无穷资源可以利用的公司会专注于一种硬件架构?答案是他们只想做一件事,并把它做好。那就是集中资源打造出出色的统一架构:既可通过扩展用于满足不同应用需求,同时还可让客户基本无需重新设计,就可以轻松地把同一架构用于多个应用。” Myron 表示,对赛灵思来说当

- 可扩展的嵌入式网络平台(07-07)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 如何快速启动嵌入式系统开发(01-06)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 设计可靠性: MTBF—这只是开始!(09-17)

- 将SoC平台设计与DSP系统生成器相集成(07-01)