如何让7系列FPGA的功耗减半

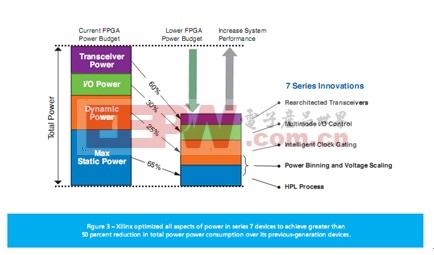

然也是如此。“通过为 7 系列 FPGA 选择通用架构,我们可以让我们的软件工程队伍专注于优化结果质量,无需分心于多个产品系列。无独有偶,我们的客户也强烈希望用类似的方式来优化 IP 核重用。与跨越多个不同的架构相比,维护统一架构有助于用最小的工作量实现 IP 核重用。” 在“降低静态功耗”的发展历程中,赛灵思采用高介电层金属闸 (HKMG) HPL 工艺仅仅是迈出了第一步,而调整 7 系列器件架构,则又迈出一步。在此前的 FPGA 产品中,赛灵思允许用户采用电源门控技术来关断未使用的收发器、锁相环 (PLL)、数字时钟管理器和 I/O。而在 7 系列 FPGA 中,设计人员可以用同样的方法来禁用未使用的 block RAM 模块。由于block RAM 模块的漏电流占给定器件总漏电流的 30% 之多,因此电源门控技术确实能起到明显的效果。 降低系统总功耗 Myron 说,虽然选用高介电层金属闸 (HKMG) HPL 芯片工艺已经显著降低了静态功耗和动态功耗,但赛灵思又进一步采取措施来减少 7 系列器件的系统总功耗,即从由静态漏电流、动态功耗、I/O 功耗和收发器功耗组成的系统总功耗入手(见图 3)。 图 3 – 赛灵思通过优化 7 系列器件的各项功耗,使其相对前代器件而言,总功耗降低一半以上 图中文字: 总功耗 目前 FPGA 功耗预算 较低的 FPGA 功耗预算 提高系统性能 收发器功耗 I/O 功耗 动态功耗 最大静态功耗 7 系列创新 重新架构的收发器 多模 I/O 控制 智能时钟门控 功率分级和电压调节 HPL 工艺 降低动态功耗 赛灵思功耗专家兼杰出工程师 Matt Klein 一直参与赛灵思 FPGA 的降耗工作。他说 FPGA逻辑的动态功耗可根据标准“CV平方f”等式计算得出: 动态功耗 = μ xfclk x CL x VDD2 等式中的“C”即电容。赛灵思 FPGA 中众多模块的架构经过精心设计,可大幅降低电容,从而能够实现较低的动态功耗。赛灵思还对部分模块的架构进行了重新设计,使之更紧凑,电容得到了进一步降低。Klein 说:“赛灵思 FPGA 中部分模块(包括 DSP48 模块)的动态功耗均低于其他 28nm FPGA 中的模块,即使是工作在高于 0.85V 的标准 1V 电压下。使用赛灵思提供的电压调节功能,还可以进一步降低动态功耗。”另外他还提到,fclk,即频率,会呈“线性方式”影响动态功耗。 Klein 说,用户也可以放大“阿尔法”,即他们的设计的活动因数,采用智能时钟门控技术来降低动态功耗。运用这种方法,设计人员可以控制给定模块的活动。但是,这种技术的实现需要花费相当长的时间,特别是在大型 FPGA 设计中,所以大多数 FPGA 用户一般不会使用。 但是 Klein 表示还有其他的办法。他说所有的 7 系列 FPGA 都有时钟分层结构,可以让设计人员在盖顶设计中编程,只启用需要的时钟资源。这样可以大幅地降低时钟负载功耗。另外,设计人员还可以分三级进行时钟门控:全局时钟门控、区域时钟门控,以及借助本地资源(比如触发器)上的时钟使能 (CE) 信号实现的时钟门控。 Klein 说:“在赛灵思 FPGA 中,每个 slice 上基本有 8 个触发器,它们共享一个通用的时钟使能端信号,不过与以往的架构不同,这个时钟使能端信号用于在本地门控时钟,同时阻止触发器翻转。现在采用这种硬件,ISE 设计工具会寻找触发器输出未被下游目标使用的情况,自动抑制不必要的开关操作。这可通过逻辑检查和后综合来完成。随后 ISE 设计工具生成本地时钟使能端信号。用户可以在映射阶段使用 -power high 或者 -power XE 选项来激活这些功能。 Klein 表示,这种自动智能时钟门控技术可将逻辑动态功耗降低多达 30%(平均达到18%)。他说:“用于生成智能逻辑门控的逻辑门数不到总逻辑门数的 1%,所以对降低动态功耗来说是个福音。” 用户还可对 block RAM 模块采用智能时钟门控技术。大多数设计人员和综合工具会把 block RAM 模块的时钟使能端置于静态的“1”。Klein 建议考虑一下有地址输入和数据输出的 block RAM 模块。输出的数据可能会被下游使用,但有时是通过被称为“sel”的多路复用器控制信号选中。首先,如果没有发生写入或者读取地址自上一个周期以来没有变动,就不必启用 block RAM 模块。其次,如果在给定周期内系统没有使用 block RAM 模块的输出,就不必为读取而启用 block RAM 模块。 与生成触发器时钟使能信号的方法类似,ISE 会自动逐周期地生成时钟使能 (CE) 信号。Klein 说:“对 block RAM 模块来说,降耗水平更为明显

- 可扩展的嵌入式网络平台(07-07)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 如何快速启动嵌入式系统开发(01-06)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 设计可靠性: MTBF—这只是开始!(09-17)

- 将SoC平台设计与DSP系统生成器相集成(07-01)