DM642在视频处理系统硬件设计的应用

从TVP5150APBS的AIP1A或AIPIB输入,数据输出引脚YOUT[0:7]与DM642的VP0[2:9]引脚连接在一起。TVP5150-APBS的系统时钟引脚SCLK与DM642的VPOCLK0引脚连接。因为在本系统的设计中采用的是ITU-R BT.656的视频输出格式,所以在系统中不需要分立的同步信号。因此,TVP5150APBS的HSYNC(行同步信号)、VSYNC(场同步信号)、AVID(行消隐指示信号)以及FIDFig.5 Colleetion bet-ween TVP5150APB5 and DM642(奇偶场指示信号)这几个引脚并不需要与TMS320DM642连接, 只需要将TVP5150APBS的INTERQ引脚与TMS320DM-642的VPOCTL0引脚连接起来。

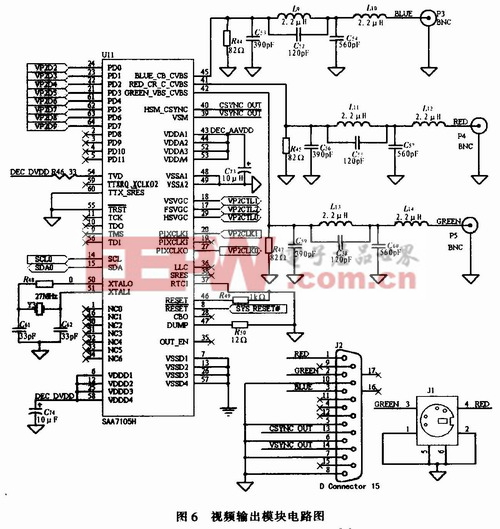

1.5.2 视频输出模块设计

在系统设计中,视频输出模块中的视频编码芯片选用的是Philips公司的SAA7105H,它同时具有SDTV(标准清晰度电视)和HDTV(高清晰度电视)信号编码能力,可以广泛用于视频输出的设计中。视频输出模块的电路如图6所示。

从图6中可知,将DM642的VP2端口配置成视频输出端口。由于VP2端口的数据线与SAA710SH的数据线相互错位,因此这会造成无法正常显示视频输出。为了解决这个问题,在将VP2端口配置成ITU-R BT.656视频输出时,数据就会从VP2 A通道的VPD02-VP2D09输出,VP2D00-VP2D 01则输出无效,因此就需要将VP2D02-VP2D09这8根数据线连接到SAA7105H的PD0-PD7对应的引脚。这样VP2D10-VP2D19在视频回放中就没有使用。

SAA7105H将从DM642端传送来的PC信号转化为PAL制式(50 Hz)或者是NISC制式(60 Hz)送到外部TV端输出。SAA7105H默认为休眠状态,在休眠过程中HC总线仍然可以接受来自DM642的命令。当SAA7105H的3个数模转换器视频输出与外部TV相连接时,SAA7105H能够自动检测到数模转换器接口的阻抗变化,然后通过芯片的TVD(电视信号检测)引脚向TMS320DM642发出中断请求,表明外部有播放要求。此时,DM642就会通过IIC总线来配置SAA7105H的内部寄存器,激活还处于休眠状态的SAA7105H,开始进行本地视频的播放。

在视频输出模块中,SAA7105H的HSVGC(水平同步输出)、VSVGC(垂直同步输出)、FSVGC(帧同步输出)分别于TMS320DM642端口的VP2CTL0、VF2CTL1以及VP2CTL2这3个引脚相连。SAA7105H的输出方式可以有RGB格式、CVBS(混合视频)格式、S-Video格式以及VGA格式等几种。其输出方式的选择通过SAA7105H的应用子地址来控制。

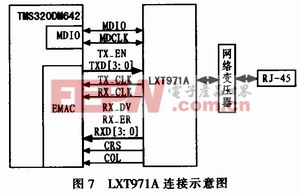

1.6 以太网接口设计

以太网接口设计中的以太网处理芯片采用Intel公司的LXT97lA,它符合IEEE标准,直接支持10 Mbps和100Mbps的双绞线应用,也可以支持100 Mbps的光纤接口。LXT971A与DM642的连接示意图如图7所示,在以太网模块中还需要用到网络变压器和RJ-45以太网连接器。

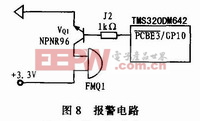

1.7 报警电路设计

系统的报警电路结构比较简单,它由驱动电路与蜂鸣器构成,驱动电路与DSP的一个GPIO引脚连在一起,电路如图8所示。

从图8中可以看出,当GP10输出高电平(通知报警)时,三极管的集电极和发射极之间将视为短接,从而驱动蜂鸣器发声报警,系统设计中采用的是有源蜂鸣器来进行报警。

2 系统调试

2.1 Flash的调试

Flash调试的步骤如下:

1)配置寄存器,Flash的基地址是0x90000000,共有512个扇区,每个扇区有4 K字节,Flash的大小为2M字节。将Flash的空间映射到TMS320D-M642的存储器空间内;

2)进行Flash的擦除操作;

3)判断擦除操作是否结束。Flash的DQ6位和DQ7位都可以用来判断擦除是否结束,这里采用的是DQ7位。在内部擦除操作过程中,读出的DQ7的值是0,一旦内部擦除操作完成,DQ7的值就会变化为1;

4)开始Flash的写操作和读操作。

可以通过CCS的Memory窗口可以观察Flash的写入是否正确。读出的数据和写入的数据经过对比后无误,说明系统的Flash工作正常。

2.2 SDRAM的调试

两块SDRAM芯片MT48LC4M3282的片选信号是与TMS320DM642的引脚接在一起的,因此SDRAM的基地址是Ox800000000.在测试SDRAM时,从SDRAM的基地址开始,长度为32 M字节。在编程时向SDRAM中写入数据。然后再读出数据,将读出的数据与写入的数据进行对比,测试后对比无误,说明系统的SDRAM工作是正常的。

2.3 静态图像的采集

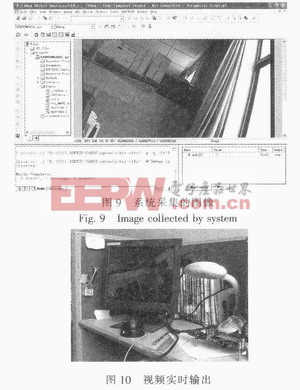

在图像采集中用到的是TMS320DM642的VP0口,需要一个CCD摄像头。采集到的静态图像通过CCS的View功能来显示。

视频解码芯片TVP5150APBS的IIC地址设置为0xB8.另外,在程序中还需要对TVP5150APBS相关的寄存器进行必要的设置以满足系统的要求。编写图像采集程序,TVP5150APBS能够实时采集图像。程序在CCS中经过编译、运行后采集到的图像如图9所示。

2.4 视频显示的调试

视频显示模块主要是在图像采集的基础上实现VGA制式视频图像的实时显示。在调试过程中

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)