DM642在视频处理系统硬件设计的应用

16 M~256 Mbit的SDRAM芯片。TMS320DM642上的Cache容量有限,所以视频数据通常存放在片外SDRAM中,在需要用到的时候通过EDMA把数据从片外搬移到片内处理,这样就可以提高程序的执行效率四。TMS320DM642的SDRAM接口图如图2所示。

由于TMS320DM642的数据总线是64位,而每片MT48LC4M3282的数据总线是32位,所以需要并联两片MT48LC4M3282才能构成64位的数据总线,这样才可以与TMS320DM642的EMW数据总线相连。参照DM642数据手册中SDRAM的配置方法,EA15、EA16控制SDRAM的组,EA3-EA14控制行地址,EA3-EA11控制列地址,片选信号接到DM642的上

![]()

,这样就把SDRAM分配到CE0空间上。

1.2.2 Flash接口设计

Flash的前身是Future Wave公司的Future Splash,是世界上第一个商用的二维矢量动画软件,用于设计和编辑Flash文档。1996年11月,美国Macromedia公司收购了Future Wave,并将其改名为Flash.在出到Flash 8以后,Macromedia又被Adobe公司收购。最新版本为:Adobe Flash Professional CS5.5.Flash通常也指Macromedia Flash Player(现Adobe Flash Player),用于播放Flash文件。

DM642 EMIFA的异步接口为各种存储器和外设类型提供了可配置的存储器周期类型,包括SRAM、EPROM、Flash等,在本系统中Flash采用的是SST公司生产的SST39VF1601 Flash,片选信号接到DM642的引脚上。当DSP上电后

![]()

,DSP通过增强的直接存储器访问从外部的CE1寻址空间复制1 K字节的数据传给内部存储空间,然后再从内部存储空间0x0处开始运行,所以Flash ROM必须配置在DSP的CE1空间,在DSP存储器中对应的地址是0x90000000-0x90200000.

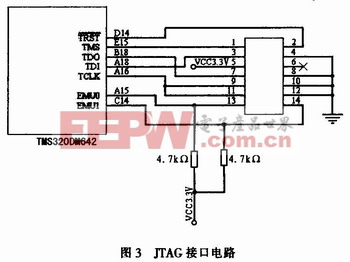

1.3 JTAG接口设计

JTAG也是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 相关JTAG引脚的定义为:TCK为测试时钟输入;TDI为测试数据输入,数据通过TDI引脚输入JTAG接口;TDO为测试数据输出,数据通过TDO引脚从JTAG接口输出;TMS为测试模式选择,TMS用来设置JTAG接口处于某种特定的测试模式;TRST为测试复位,输入引脚,低电平有效。

JTAG接口是调试环境和目标板之间的接口,它的好处是可以让开发者在对目标板进行开发的同时可以不改变目标板的系统结构,从而方便了系统的开发与测试。XDS510仿真器通过JTAG接口将系统板与电脑连接起来,这样就可以使用TI提供的集成化开发环境对系统进行调试了。JTAG接口采用标准的双排14脚插座。系统的JTAG接口电路如图3所示。

1.4 电源模块设计

DM642需要两种电源,一种是内核电源(1.4 V),另一种是I/O电源(3.3 V)。通常由于DM642用于嵌入式系统中,因此电源电路设计不仅要考虑电压精度、稳定度和外围电路的复杂度等问题,还要考虑低功耗问题。另外,根据设计要求,为了保证芯片正常工作,在系统上电作时,对这两种电源的上电顺序还有一定的要求,如果违反该要求,可能降低器件的性能或永久损坏器件。内核电源要比I/O电源早上电,至少不能晚于I/O电源上电。在电路设计中,通过采用在两个电源之间串联二极管的方法来解决系统上电顺序的问题。

系统设计中,电源芯片采用的是TI公司的TPS54310,它是TI公司生产的一款开关电源调节芯片,它能够实现低电压输入和高电流输出(输人电压范围为3~6 V,输出电压根据需要可以在0.9~3.3 V之间调节,输出电流为3 A)。图4是3.3 V电源产生电路,1.4 V电源产生电路与此类似,只需根据TPS54310中的计算公式将相应的电阻和电容值做相应的修改就可以得到1.4 V电源。3.3V的电源不仅是DM642的0电源,同时也是系统上视频解码芯片、视频编码芯片、SDRAM芯片等的供给电源。

1.5 视频输入输出模块设计

1.5.1 视频输入模块设计

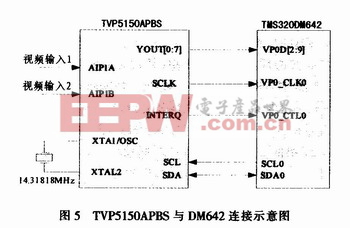

视频输入模块设计采用的视频解码芯片是TVP5150APBS,它是TI公司专门开发的一款可以方便携带的低功耗视频解码芯片,可以广泛用于视频系统的设计。TVP5150APBS的视频输入端可以输入两路复合视频信号或者一路S端子信号。输入信号(如PAL、NTSC等制式)通过增益控制单元、模数转换器和Y/C分离及处理模块后,最后可以转化为8位ITU-R BT.656的数据格式,或者转化为8位4:2:2的数据格式。TVP5150A-PBS的初始化操作是通过操作IIC总线来实现的。TVP5150APBS的IIC地址可以通过控制12CSEL引脚的高低电平来设置。当该引脚是低电平时,IIC地址是0xB8h,当该引脚是高电平时,IIC地址则为0xBAh.TVP5150APBS与TMS320DM642的连接示意如图5所示。

从图5可知,视频信号可

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)