JavaCard指令处理器的FPGA设计

时间:01-30

来源:互联网

点击:

寄存器MCP得到新的JavaCard指令对应的微码序列首地址,MCP的变化使微码指令寄存器MCR变为该微码序列的首个微码指令,再由微码处理器执行此MCR中的微码。

4 JavaCard CPU测试平台的FPGA实现

4.1 外围接口和模块

测试平台是以一块xc2s200芯片为核心的简单开发板,全部设计都在此芯片内实现,包括CPU逻辑、存储单元等,板上的8位led指示灯用作I/O输出端口。

4.2 测试平台框架

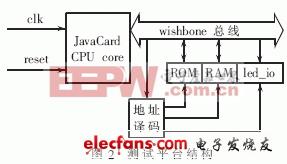

测试平台框架结构如图2所示。

4.3 结果说明

设计是用Verilog语言实现的,内部使用16位数据总线,对外是8位的wishbone总线,微码ROM为4KB,外接512B的ROM和512B的RAM。

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)