JavaCard指令处理器的FPGA设计

1 JavaCard简介

智能卡是指集成了CPU、ROM、RAM、COS(芯片操作系统)和EEPROM,能储存信息和图像,具备读/写能力,信息能被加密保护的便携卡。智能卡的最基本标准是ISO/IEC7816。智能卡在银行、电信等行业得到广泛应用,但在发展过程中也遇到很多问题,主要有:各厂商指令集不统一;编程接口APIs太复杂;开发环境不通用,新卡开发都要熟悉开发环境;系统不兼容,专卡专用。由于开发门槛过高,影响了智能卡的发展。市场对智能卡的发展提出了新的要求,Sun公司提出了Java Card开放标准。JavaCard技术将智能卡与Java技术相结合,克服了智能卡开发技术太专业、开发周期长等阻碍智能卡普及的缺点,允许智能卡运行Java编写的应用程序。JavaCard技术继承了Java语言的优点,制定了一个安全、便捷且多功能的智能卡平台。

JavaCard基本的硬件配置(来自Sun文档)为:512B RAM、24KB ROM、8KB EEPROM、8位处理器。典型的JavaCard设备有8位或16位的CPU,3.7MHz时钟频率,1KB的RAM和大于16KB的非易失存储(EEPROM或Flash)。高性能的智能卡带有独立的处理器、加密芯片及密码信息。

JavaCard系统的实现有基于软件虚拟机和基于硬件两种方法。基于软件虚拟机方法是在非Java处理器上用软件方法模拟实现JavaCard平台,在此平台上实现JavaCard应用。基于硬件方法是硬件逻辑实现JavaCard处理器,在此硬件基础上实现JavaCard平台,再在此平台上实现JavaCard应用。

2 Java处理器的实现方式比较

Java处理器有以下几种实现方式:

(1)通用CPU+OS+Java软件解释器,软件解释执行Java指令。

(2)通用CPU+OS+Java JIT(Just-In-Time)编译器,按块编译执行Java指令。

(3)Java加强CPU+OS+特殊的Java编译器,充分使用Java加强硬件的优势。

(4)Java 硬件CPU,本地支持Java指令,执行效率最高。

目前的Java系统是基于软件虚拟机实现的,软件解析执行Java指令,如(1)、(2)。用软件实现JavaCard虚拟机,需要软件JavaCard指令解释器,将Java指令转换到本地CPU的指令集。这样,不但速度慢,而且虚拟机本身占用内存资源,不适合在智能卡这种资源有限的硬件中应用。方式(3)要求CPU硬件实现部分Java指令,它需要特殊的编译器来充分发挥Java加强CPU的功能。方式(4)是最有效的解决方法,Java指令的执行不再需要先转换到宿主CPU的本地指令集,同时,它也不占用RAM等软件资源,可以给应用程序提供更多的资源。

本文介绍JavaCard CPU。系统采用Verilog描述,设计成一个配置灵活、修改方便、资源占用少、兼容性好、可以在普通FPGA中实现的软核。

3 JavaCard CPU的设计

3.1 Java CPU的硬件实现技术

在CPU的设计中,当从内存中取出下一条指令时,执行这条指令有两种方法,即硬件逻辑方法和微码序列方法。硬件逻辑方法使用译码器、锁存器、计数器和其他一些逻辑部件转移和操作数据,完成指令功能。微码序列方法是在内部实现一个非常简洁、快速的微码处理器。此微码处理器的每条指令对应很简单的硬件动作(一般都是单周期指令),将要执行的CUP指令作为索引,索引到微码ROM中的某个地址,通过执行此地址处的一组微码完成指令功能。

硬件逻辑方法的优点是能设计出更快的CPU,缺点是难以实现复杂的指令集,同时会导致芯片面积增大。微码序列方法的优点是可以减小芯片的面积,实现复杂指令集,缺点是速度有时较慢。两种方法的速度快慢并非绝对,微码指令是简单指令,一般每个时钟就能执行一条指令。硬件逻辑方法在执行CPU指令时,通常也是划分为几个阶段执行,同样需要几个时钟。实际设计中采用哪种方法要权衡利弊,在速度不是关键时,微码序列方法是个很好的选择。

3.2 JavaCard CPU结构

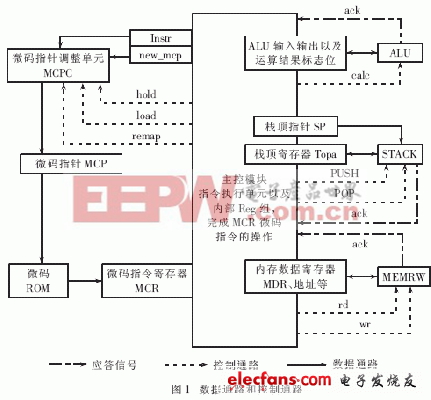

JavaCard CPU采用微码实现,核心部分是微码处理器,用微码指令序列实现JavaCard指令。微码处理器主要组成为:主控逻辑CORE,运算单元ALU,内部堆栈单元STACK,微码ROM,微码指令指针调整模块MCPC,外存读写接口MEMRW,通过wishbone总线连接外部RAM、ROM、I/O。各模块之间连接关系、数据通路、控制通路以及应答信号连接见图1。

3.3 微码处理器各模块接口及功能

(1)运算单元ALU

module alu(x,y,op,z,flag,calc,rst,ack,clk);

x、y为输入操作数,op为操作码,z为输出结果,flag为输出运算结果标志,calc为运算使能控制信号,ack为运算结束应答。本模块完成op定义的运算,并给出标志位和应答。

(2)内部堆栈STACK

module stack(clk,rst,pop,push,data_i,data_o,sp,ack);

pop、push为堆栈的弹出及压入操作信号,data_i、data_o为数据输入输出,sp为堆栈指针,ac

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)