基于80C196KC单片机的电力补偿装置控制系统设计

电力补偿装置是对电网实施无功补偿,提高电网的功率因数,让无功功率基本就地平衡,降低线损,改善电压质量和提高线路及变压器的输送能力。目前在电力补偿系统中有多种补偿方法,本文中的补偿系统是根据寻优负序电流最小进行补偿的。系统计算需要对交流电一个周期20 ms内对单相电压u、电流I进行采样,要求一个周期内采样次数至少在100次以上。针对这一特点,设计了基于80C196KC的控制系统。Intel公司的高性能16 b单片机80C196KC,其运算速度快,能够满足系统高速采样的要求。

1 系统硬件设计

本系统的硬件部分主要由采样输入电路、中央控制单元、程序存储单元、输出驱动电路4部分组成。系统总体框图如图1所示。

1.1 模拟输入电路

系统中数据采集所使用的传感器为电压互感器和电流互感器,需要分别采集三相的电压和电流,共需要六路输入。80C196KC内有一个逐次逼近型的A/D 转换器,共有8个输入通道。其输入引脚ACH0~ACH7与P0.0~P0.7共享。内部的A/D转换器8 b/10 b可调,自带采样、保持电路,这样减少了外围电路,也减少了干扰和干扰源,增加了系统的稳定性和抗干扰性,并且减少了控制板的尺寸。在本系统中采用10 b转换方式。

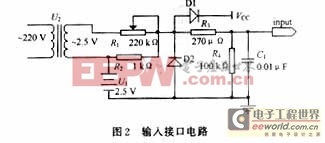

为了保护A/D转换器,增加可靠性,在A/D通道的输入端,可采用如图2所示的输入接口电路。

其中2个二极管D1和D2起过载保护作用,当输入电压高于VREF+0.7 V左右时,D1导通,输入电平被箝位在VREF+0.7 V的水平上;当输入电压低于-0.7 V的水平上。这种过载往往是尖峰干扰,持续时间很短。MCS-96的技术条件规定模拟输入端对模拟地ANGND的电压不能低于-0.3 V,这一点可靠输入端的低通滤波器R4和C1来保证。图中此滤波器的时间常数τ=R4C1=270×0.01=2.7μs,若以-0.7 V作为此滤波器的阶跃输入,则此滤波器输出端(即80C196KC的模拟信号输入端)达到-0.3 V的电平需耗时:

t=-τln(1-0.3/0.7)=1.15μs

而通常这类尖峰噪声的峰值持续时间远小于上述时间,因此,这一输入电路可有效地起到过载保护作用。

1.2 中央控制单元

80C196KC是CHMOS高性能16 b单片机中的一个新分支,内部EPROM/ROM为16 b,内部RAM为488 b,有24 b的专用寄存器。80C196KC中采用了“垂直窗口”结构,使得新增的256 b RAM通过窗口映射同样可以作为通用寄存器来访问。80C196KC可以采用16 MHz的晶振,内部时钟是2分频,其运行速度比12 MHz的80C196KB快33%,比12 MHz的8096BH快1倍。最小电路是指能使单片机工作而所加的最少的外围设备,一般包括复位电路和晶振。80C196KC的最小电路如图3所示。

1.3 输出单元

输出共有12路,其中 P1.0~P1.3控制A相,P1.4~P1.7控制B相,HSO.0,HSO.1,P2.6,P2.7控制C相。输出经过光控可控硅MOC3061进行隔离,又经一级双向晶闸管驱动后,加在双向晶闸管的控制级,控制双向晶闸管的导通,进而控制电容器的投切。输出电路如图4所示。

从80C196KC的输出管脚输出的信号电流只有几个μA,不足以驱动后边的光电耦合器,所以加一个TTL芯片5407作为电流驱动元件。MOC3061是常用的双向晶闸管输出的光电耦合器,他的输出端是光敏双向晶闸管,当光电耦合器的输入端有15 mA电流流入时,晶闸管即导通。MOC3061的输出端还配有过零检测电路,用于控制晶闸管过零触发,以减少用电器在接通时对电网的影响。

2 软件设计

系统的软件采用了高级语言PL/M-96嵌入汇编语言编写,采用模块化结构设计。对于实时性要求较高的部分如A/D转换部分,由于汇编语言具有灵活性好、代码转换速度快等特点,同时80C196KC的指令系统效率高,执行速度快,因此采用汇编语言来编写A/D转换程序,其他部分采用高级语言编写,程序可读性好。

整个软件共包括7部分,他们分别是:主程序、A/D转换子程序、投切子程序、电压投切子程序、电流计算子程序、输出子程序、软件定时器中断服务程序。下面介绍主程序及A/D转换子程序的设计。

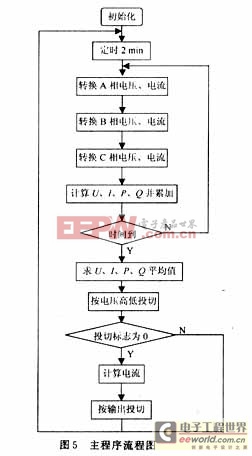

2.1 主程序设计

主程序流程图如图5所示。

2.2 A/D转换子程序

数据采样是通过A/D转换与软件定时器的中断服务程序相结合完成的。每个周期测量开始由主程序确定模拟通道;用软件定时器定时,然后启动A/D转换。软件定时器定时时间到进入软件定时器中断服务程序,由软件定时器中断服务程序中返回主程序完成一个周期的采样过程。

A/D转换子程序流程图如图6所示。

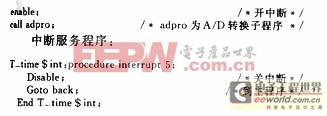

系统中软件定时器中断子程序是采用高级语言PL/M语言来编写的,附程序如下:

定时20 ms程序:

hso_command=18h;/*采用软件定时器0,中断方式*/

hso_time=timer1+15000; /*定时20 ms*/

3 结 语

- 基于80C196KC的ARINC429总线接口板设计(10-24)

- 基于三相可控硅的半控桥数字触发器设计(08-18)

- 一种基于80C196KC的电子软起动器的软硬件实现(04-05)

- 基于80C196KC与PSD4235G2在线编程的实现(03-28)

- 80C196KC-ADMC401双CPU接口电路设计/其应用(03-23)

- 基于80C196KC与PSD4235G2在线编程的实现 ((03-13)