基于PowerPC的单板计算机的设计

摘要: 本文主要介绍了基于PowerPC G4系列的低功耗、多数据并行处理的单板机的设计方法,讨论了硬件设计中需要注意的事项和VxWorks 环境下BSP的调试方法,高度的扩展性和丰富的接口设计使得系统有较好的应用价值。

1 引言

随着科学技术的发展,嵌入式处理器在通信设备、消费电子、军用电子等领域有了广泛的应用,而且对处理器的处理速度、功耗及工作温度都有了更加严格的要求,尤其在汽车电子、军用电子等方面的应用。

PowerPC 体系结构是一种精简指令集计算机(Reduced Instruction Set Computer,RISC)体系结构,具有高性能和低功耗的特点,主要应用在嵌入式系统中,可以作为单板计算机,进行高性能计算和图像处理。

在PowerPC 家族中,现在应用最为广泛的是G4 系列, G4 对G3 的重大改进有两个,第一是支持对称多处理器(SMP)结构,第二是G4 引入了一流的AltiVec 技术来处理矢量运算。

AltiVec 技术是一个128 位的SIMD 矢量处理引擎,据Motorala *估可以使性能提升到原来的4.3 倍。

本文以PowerPC G4 主机处理器为例,介绍标准6U 高度CompactPCI 单板计算机的硬件设计以及实时操作系统VxWorks 的BSP 开发过程。

2 单板计算机硬件开发

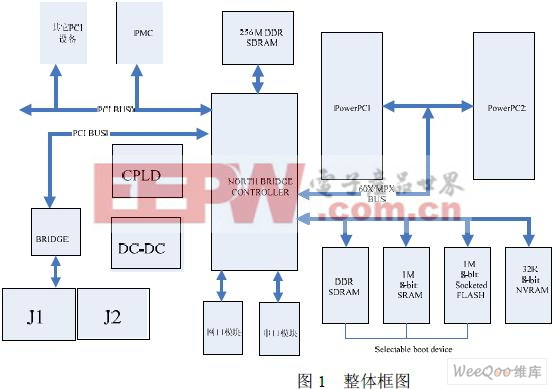

单板计算机的整体框图如图1 所示。

整个单板的设计分为三个部分:电源模块,PowerPC 部分和通信接口部分。其中PowerPC 部分和外围接口以PCI 总线为分界线,PowerPC 部分包括PowerPC、host bridge、SDRAM 和FLASH。

外围接口包括网口、串口、通过PCI 总线扩展的接口和扩展的二级PCI 总线。网口和串口在开发阶段用于单板和开发主机通信,并能在单板嵌入操作系统后作为多个单板之间的通信接口。框图中PowerPC 没有指定具体的型号,可以选择IBM 的如PPC750, 也可以选择Freescale的如PowerPC G4 系列的MPC74XX,host bridge 可以选择MARVELL 公司的MV64360 或MV*60。用户可以根据的不同需要选择相应的组合。

2.1 电源模块的设计

电源是任何一个电路系统至关重要的部分,所有的信号传输都是基于准确而稳定的电源基础上的。CPCI 连接器提供的电源有5V、3.3V、12V 和-12V,整个单板上需要的电源有多种:主电源5V、PowerPC 的内核电源、host bridge 内核电源、DDR SDRAM 电源和其余I/O总线电源3.3V。对电流需求大,电源稳定性要求高的,应采用可编程的DC/DC 控制芯片完成电源的转换。

电源模块的PCB 布板也要进行小心处理, 主要有以下几个方面需要注意。

a) 放置去藕电容:随着一定数量的去藕电容被放置在板上,电路板本身特有的谐振可以被抑制掉,从而减少噪声的产生,还可以降低电路板边缘辐射以缓解电磁兼容问题。为了提高电源供电系统的可靠性和降低系统的制造成本,应考虑如何经济有效地选择去藕电容的系统布局。

b) 降低电源供电系统的阻抗:一个低阻的电源供电系统(从直流到交流)是获得低电压波动的关键:减少电感作用,增加电容作用,消除或降低那些谐振峰是设计目标。为达到此目标应降低电源和地板层之间的间距; 增大平板的尺寸;提高填充介质的介电常数;采用多对电源和地板层。

2.2 PowerPC 部分

PowerPC 部分包含PowerPC12,host bridge,DDR SDRAM,SRAM 和Flash。此部分是整个单板计算机的核心,电路设计调试难度也最大PowerPC12 和DDR SDRAM 部分速度较快,电路设计要注意PCB 布线选择合适的拓扑结构和布线策略, 以保证信号完整性。

a) 拓扑结构的灵活应用

在 PCB 设计中常用的拓扑结构有菊花链拓扑和星形拓扑。要根据不同的情况采用不同的拓扑结构。

一般而言,对于多负载的总线系统常采用菊花链拓扑,并在最远端的负载处进行适当的终结。菊花链拓扑的优势在于易于进行阻抗控制,端接简单,网络的布线长度短,布线较为方便,只要各个接收器在接收信号时间上的差别在允许的范围内就可以采用菊花链拓扑进行布线(这也说明菊花链拓扑不适用于高速系统),注意要让菊花链的分支线尽量短。Local bus 上的外设我们是用的此种拓扑结构,local bus 上有Flash、DDR SRAM、SRAM 等外设。

星形拓扑一般在时钟网络或对信号同步要求高的网络中应用,其共同点就是要求各接收器在同一时刻收到驱动端发来的信号,星形拓扑的布线难度比菊花链拓扑的要大,占用空间也大。实际的星形拓扑会存在端接传输线分支,驱动器与公共节点间存在传输线分支,这些都会劣化信号,所以在设计星形拓扑一般需要仿真,以保证信号的完整性。

PowerPC12(U1、U2)和host bridge(U3)采用星形拓扑结构,其后仿真图形如图2 所示,基本满足信号完整性。时钟电路采用星形拓扑结构,

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)