����FPGA���TMS320C54K/SDRAM�Ľӿ�����

�ڣģӣ�Ӧ��ϵͳ�У���Ҫ���������洢��������������������磬�����������������У�Ϊ�˽��ֳ���������ͼƬ��ͼ���ݴ���������Ҫ���ģӣд����������ת�Ƶ�������Ա����á���Ŀǰ�Ĵ洢���г������ӣģң������������ܼ۸�ȵ����ƣ������ģӣп��������������ģӣ���ӣģң���ֱ�ӽӿ��Dz����ܵġ��ƣУǣ�(�ֳ��ɱ��������)���������ʹ����ִ���ٶȿ졢�������߷ḻ���ص��Խ��Խ��س������ִ���·����С������ãƣУǣ���Ϊ�ӿ�оƬ���ṩ�����źźͶ�ʱ�źţ���ʵ�֣ģӣе��ӣģң��͵����ݴ�ȡ��

�� �ӣģң��ͽ���

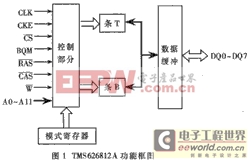

���IJ��õģӣģң���Ϊ�ԣͣӣ�������������TMS626812A��ͼ��Ϊ�书�ܿ�ͼ�����ڲ���Ϊ������ÿ�������ֽڣ����ݿ���Ϊ��λ���ʴ洢������Ϊ�����ֽڡ�

|

����������������������ʱ�ӣạ̃������ص������½��еģ�ˢ��ʱ�ӽ���ˢ���ڲ��������ң��͡��ԣͣӣ���������������Ҫ������������������ǣ�������е�ַ��ڡ��е�ַ��ڣ�д�������е�ַ��ڣ�������������Ч���Զ�ˢ�¡�����ˢ�¡��ӣģң�����ԣͣӣ������ã�����TMS320C54X�ӿ����õ���������Ҫ�У� �ͣңӡ� �ģţ��á� ���ãԣ֡��ףңԣ��С��ңţ��ģ��кͣңţƣҡ�������Ŀ�ľ��Dz��������ź���������Щ�����ʱ��Ҫ���ڣԣͣӣ��������������ľ���˵�����Բ鿴�������ֲᡣ

�� �ӣģң�����ԣͣӣ������ã�����֮���ͨ�ýӿ�

ͼ���ǣģӣ���ӣģң��͵�ͨ�ýӿڿ�ͼ��ͼ�Уģӣ� �ɣ��ƴ����ԣͣӣ������ã������˽ӿڵ�Ԫ���ӣģң��� �ãΣԣ� �����ӣģң��� �˽ӿڿ��Ƶ�Ԫ���ӣģң��ͱ����ó�һ���Զ�д���������ֽڣ����ģӣ�һ��ֻ��дһ���ֽڣ���������������������£����£����������ת���ݡ��£����£���С��Ϊ�������ֽڣ�����ӳ�䵽�ģӣ��е�ͬһ��ַ�ռ䡣

|

���ܣ£����£���Ӧ��ͬһ��ַ�ռ䣬��������������������ͬһʱ�̽��кϷ����ʡ�ʵ���ϣ����£����ģӣз���ʱ���£��ͱ��ӣģң��ͷ��ʣ���֮Ҳ���������ģӣ���£�д���ݣ��ӣģң��;ʹӣ£������ݣ������ӣģң��͵�����д���£���ʱ���ģӣоʹӣ£������ݡ�����ͬʱ��ͬһ����������д�������������ϱ�����������ת�Ʒ�ʽ�����ֺô���һ�Ǽ����ˣԣͣӣ������ã������ķ����ٶȣ����ǽ���˶���֮���ʱ�Ӳ�ͬ�����⡣

�� �ƣУǣ��е�Ӳ�����

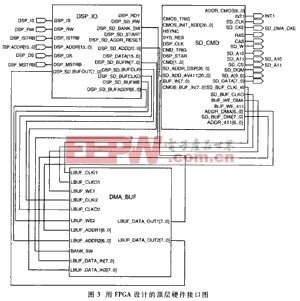

�ԣͣӣ������ã�����Ϊ�ⲿ�洢������չ�ṩ�������źŦ��ạ̃ˡ��ãӡ����������������ģ����ģ������ңס��ͣӣԣң¡��ɣӣԣң¡��ɣӢ����ӣģң��ͽ��������źŦ��ạ̃ˡ��ãˣš��ãӡ��ģѣ͡��ס��ң��ӡ��ã��ӡ����������������������˿����źŲ�ͬ����Ҫ�ڣģӣ���ӣģң���֮����Ͽ��������Ա㽫�ӣģӣй������źŽ��ͳɣӣģң����ܹ����յ��źš�ͼ�����ãƣУǣ���ƵĶ���Ӳ���ӿ�ͼ��

|

ͼ����Ҫ������ģ�飺�ģӣУ��ɣϡ��ģͣ��ߣ£գƺͣӣģ��ãͣġ����УģӣУ��ɣ��ǣģӣж˵Ľӿڣ���������ԣͣӣ������ã��������͵ģӣģң��͵�ַ������ģͣ��ߣ£գƴ����������£����£����ӣģߣãͣ�ģ�����������ӣģң��ͷ�������ĸ����źš�

�ģӣУߣɣ�ģ���ְ����ɣϣߣģͣ����ģӣУߣ£գƺͣģӣУ�

�ңţ��ġ��ɣϣߣģͣ������ӣģң��͵������źŢ���ͼ���еģģӣУߣңģ١��ģӣУߣӣģߣңס��ģӣУߣӣģߣ£��Σˣߣӣס��ģӣУߣӣģ�

���ģģҤ����������������ģӣУߣӣģߣ��ģģңߣңţӣţԡ��ģӣУߣӣģߣӣԣ��ңԡ�

�ģӣУߣ£գƲ������ʣ£����£��ĵ�ַ�����ݺͿ����źţ�ͼ����ָ�ģӣУߣӣģߣ£գƣạ̃ˣɡ��ģӣУߣӣģߣ£գƣạ̃ˣϡ��ģӣУߣӣģ�

�£գƣףš��ģӣУߣӣģߣ£գƣ��ģģҤ��������������ģӣУߣӣģߣ£գƣɣΤ��������������ģӣУ��ңţ�����ģ���������ƣģӣеĶ�д����

�ģͣ��ߣ£գƷ�Ϊ�£����£������������������������ݴ��͢�ÿ������������������źŰ������ạ̃ˣɡ��ạ̃ˣϡ��ףš����ģģҤ������������ģ��ԣ��ߣɣΤ������������ģ��ԣ��ߣϣգԤ�����������

�£��Σˣߣӣ���һ�������źŢ����ڣģӣкͣӣģң��Ͷԣ£����£����л����ʡ�

�ӣģߣãͣ�ģ�����ˢ�¡�����д���ܡ����ģӣ�оƬ�����ӣģң��Ͷ�����ʱ���������ֽڵ����ݴӣӣģң����ж����������洢���£���£��У����ģӣз���д����֮ʱ���������ֽڵ����ݴ����£���£�֮�в�������д���ӣģң����С�

�� �������

�ԣͣӣ������������� �ӣģң����������ֽڵĴ洢���������ԣģӣ��������ɣ��ϵ�ַ��ƣУǣ����ͷ��ʣӣģң��͵ĸߵ͵�ַ�������Т��������ɣ��ϵ�ַ��Ӧ��ͼ���еģ����裟�ģͣ��ߣ��ģģȣ��ͣ����裟�ģͣ��ߣ��ģģ̣������⣬����һ���ɣ��ϵ�ַ��ͼ���еģ����裠������ƣУǣ�������������ӣģң��ͷ��ʵ��źš�

�ģӣ���ӣģң���д����ʱ�IJ����������£�

FPGA TMS320C54K SDRAM ������£�

- �ڲ���FPGA���DSPϵͳ�з������Ҫ�� (06-21)

- ���� DSP Builder��FIR�˲����������ʵ��(06-21)

- ����FPGA�Ŀ��ٲ���FFT�����ڿռ�̫����Զ��ͼ������ϵͳ�е�Ӧ��(06-21)

- 3DES�㷨��FPGA����ʵ��(06-21)

- ��FPGAʵ��FFT�㷨(06-21)

- FPGA��DSP���ܽ���(06-16)