FPGA与外部存储设备的接口实现

|

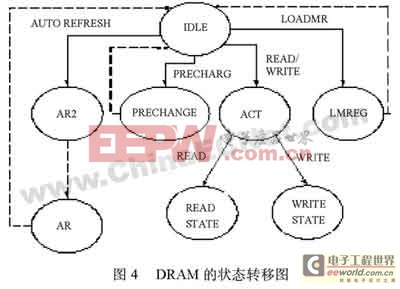

其次,是如何控制DRAM的各种状态。当设计FPGA与DRAM的接口时,由于它除了读写状态外还有较多的其它状态,所以需要着重设计好读写状态与其它状态之间的转换控制。为了解决这个问题,本设计采用了状态机来控制这些状态之间的关系,DRAM的状态转移图如图4所示:

下面给出了图中各个状态所表示的意思:

IDLE 表示存储器处于空闲状态;

LMREG 表示加载寄存器状态;

ACT 表示活动状态;

AR2 表示自动刷新有效状态;

AR 表示自动刷新无效状态;

WRITE STATE 表示读状态;

READ STATE 表示写状态;

只有当系统时钟的上升延到来时,才会触发这个状态机改变一次当前状态。

|

刚开始时,存储器的初始状态为空闲状态,当有请求来时才会进入下一个状态,如果没有请求就一直保持空闲状态。虚线表示自动按顺序进入下一个状态。

最后,是FPGA的设计要求。一个优秀的FPGA设计不仅要达到系统的基本要求,同时必须满足可读性、可重复性和可测性。

可读性好的FPGA设计原理图和硬件描述语言设计应该包含足够详细的注释。每张原理图之间的关系及硬件描述模块间的互联关系的说明固然重要,但是每个模块本身的说明也是不能忽视的,例如状态机的文档应当包括状态图或功能描述。好的文档也许花不了很多的时间,但是却可以在调试﹑测试和维护设计上节省大量的时间。

可重复性指FPGA设计应该保证如果不同的人从不同的部位开始,并重新进行布局布线等,应该得到同样的结果。没有这个保证,验证以及其他形式的设计测试就毫无意义。设计者显然不希望在设计里出现这样的情况,具有相同的输入输出管脚和功能的器件,由于布局布线的差异,导致最后时序不一致。如果在实现的过程中,系统设计软件的参数或选项不一致,就会发生这种情况。因此FPGA的文档就应该包括必要的信息,即软件开发系统的版本号﹑软件的各个选项及参数设计。

可测性是FPGA设计的最后一个特征。系统级的测试要求设计者对整个设计流程及系统架构都要很清楚。随着设计层次的提高,使得设计者面对的电路规模越来越大,功能越来越复杂,相应电路的测试也变得越来越困难。在设计过程中综合考虑测试的设计问题并统一实施,将有效地缩短整个产品的开发时间、减少返工。

结束语

在开发过程中由于采用高级硬件编程语言-编程器件的设计实现过程,大大缩短了开发周期,增加了硬件设计的灵活性和可移植性,也避免了专用集成电路设计的高风险。采用逻辑仿真与后时序仿真相结合的验证方法,可以保证设计的可靠性。基于上述优点,这种开发方式在中小型集成电路开发中已得到广泛应用。 随着工艺技术的发展与市场的需要,超大规模﹑高速﹑低功耗的新型FPGA将会不断推陈出新。现在新一代的FPGA甚至集成了中央处理器(CPU)或数字处理器(DSP)内核,在一片FPGA上进行软硬件协同设计,为实现片上可编程系统(SOPC,System On Programmable Chip)提供了强大的硬件支持。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)