采用WCDMA速率适配算法的FPGA设计

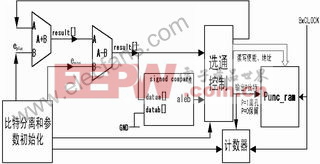

图4 凿孔图样产生

该结构工作过程如下:首先,比特分离和参数初始化模块主要完成模块计数和eini、eminus、eplus等参数的初始化设置。

在减法器端,当前误差值e减去eminus,该数值同时送给数值比较器和选通控制模块。减法器的输出结果和0值作比较,如果结果小于零则记P比特为1;如果结果大于零则记P比特为0,同时将减法器的输出结构作为当前加法器的A端输入值。P比特则在选通控制模块产生的读写使能、地址信号线的驱动下写入Punc_ram。另外用一个计数器来对比特数进行记录,以控制整个流程的结束时刻。系统时钟为8倍码片时钟,计数器和Punc_ram都采用同步控制,加法器、减法器及比较器都不采用同步时钟延时。

保留比特搬移转换模块

凿图样产生以后,接下来的操作就是保留比特的搬移和转换,并进行第一次交织和无线帧分段。按照3GPP协议,对于TTI=20ms的144Kb/s业务,其交织模式是0,1>,亦即顺序输出。

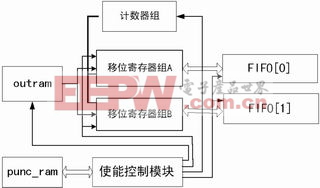

图5 保留比特搬移转换

实现的流程图如图5。假定TURBO编码后待的比特流存在out_ram中,这里进行的操作关键是凿孔图样的读出和out_ram的读出应该是同步一致进行(在同一个时钟上升沿开始),用Punc_ram的输出来作为积攒比特的使能信号。用移位寄存器组和计数器实现比特积攒,每等到满16bit时,就进行串并转换,同时产生一个fifo写使能脉冲,把一个字的内容写入fifo;等到满一帧(复接前的数据帧)的时候,转向对下一个fifo进行写操作。到一个数据帧4205bit结束时,积攒比特不满16的补零表示,串并转换为一个字写入fifo。

资源使用和时延分析

按照上面的实现方式,主要占用的是存储资源,现代FPGA中的ESB(嵌入式系统块)可以很容易地实现各种类型的存储模块,包括双端口RAM、ROM、FIFO及CAM块。下面主要进行的是时延分析。

按照上面的流程可以大致估算一个比特从“凿孔”图样产生到比特搬移完成所用的时间。所选工作时钟速率为8倍码片速率3.84MHz,一个时钟周期约为32.4ns。凿孔图样模块中的加法器、减法器、选通控制大概需要3个时钟周期,9516个凿孔图样的产生需要大致925ns;保留比特搬移模块主要是数据比特的直接搬移,对于最后一个比特而言,假定它是保留比特,从搬移开始到最终写入FIFO,经过了大致9516+16=9532个时钟周期,耗时大约308ns。对整个流程用MAXPUSII仿真,总共耗时1.336ms,考虑到中间的缓冲控制和使能控制延迟,仿真结果和计算值大致吻合。对于TTI=20ms的业务,完全满足处理要求。

结语

WCDMA系统的电路型数据业务(64K)和分组型数据业务(144K、384K)可以实现对多媒体业务的承载,但由于基带数据处理量大、比特搬移操作明显,编码复接中的核心算法之一速率适配算法我们采用了FPGA实现,并且适当合并了前后步骤,大大缩短了处理时间,使系统达到了很高的吞吐量和处理速度,完全满足3GPP协议规范的要求。在实际实施中被证明是可行的。此外,文中提出的模块合并、产生凿孔图样进行比特积攒搬移的思想同样可以适合未来更复杂的编码复接方案。

FPGA 设计 算法 适配 WCDMA 速率 采用 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)