基于可编程逻辑器件和A/D转换器的高速数据采集卡方案设计

始,同时,当启动读出地址控制信号到达时,对当前读出地址加1,加满之后清零并重新开始。

(4)PCI接口控制模块

PCI总线接口控制模块中的信号按照功能可以分为系统信号、地址和数据信号、接口控制信号等。系统信号包括CLK和RST两个信号,为系统提供时钟和复位。对地址和数据信号来说,在总线传输操作周期中,一个PCI总线周期由一个地址段和紧随其后的一个或多个数据段组成,其中AD[30:0]是地址和数据复用总线,它可为PCI接口电路提供地址和数据信号。复用引脚C/BE[3:0]为PCI接口电路提供总线命令和这节允许两组信号。

接口控制信号主要由FRAME、IRDY、TRDY和DEVSEL等组成。其中FRAME信叫是总线周期构成信号,由当前总线中主要设备驱动,用以表明一个总线风吹草动期的开始和延续;IRDY表明启动方准备好数据;TRDY是目标设备就绪信号,在写操作中,TRDY有效说明从设备已准备好接收数据,在读操作中,它说明AD[30:0]上已有有效数据;DEVSEL为设备选择信号,当其有效时,说明驱动它的主设备已将其地址译码作为当前操作的目标设备,该信号作为输入信号时,DEVSEL用来表示总线上已有目标设备被选中。

其他PCI总线所需但本系统不用的信号则可用高阻态来代替。图5示出PCI接口控制模块的内部结构。

PCI总线上的基本传输机制是突发分组传输。一个突发分组由一个地址周期和一个(或多个)数据周期组成。PCI支持存储空间和I/O的突发传输,所有的数据传输基本上都是由FRAME、IRDY和TRDY三条信号线控制的。

当数据有效时,数据资源需要无条件设置IRDY信号(写操作为IRDY,读操作为TRDY)。接收方可在适当时间发出它的xRDY信号。FRAME信号有效后的第一个时钟上升沿是地址周期的开始,此时传送地址信息和总线命令。下一个时钟上升沿即是一个(或多个)数据周期的开始,每当IRDY和TRDY同时有效时,所对应的时钟上升沿,数据可以在主、从设备之间传送。在此期间,可由主设备或从设备分别利用IRDY和TRDY的无效而插入等待周期。PCI总线的读写时序如图6所示。

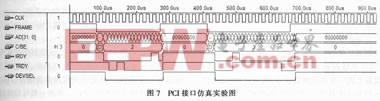

本设计采用Verilog语言来进行编程,在MAXpluse II仿真平台上进行仿真,采用的电中是Altera公司的EPM7160SQC160-6。PCI接口控制部分的仿真结果如图7所示。

3 结束语

本文提出一种采用可编程逻辑器件和A/D转换器组成的高速数据采集卡的设计方案,该采集卡只用两块主体电路,因而结构简单,可以直接插入PC,适用于智能仪器和其他需要高速数据采集的场合。如果在该采集卡前置处理部分增加通道转换和可控放大部分,则该采集卡的功能将更加完美。

高速 数据采集 方案设计 转换器 A D 可编程 逻辑 器件 相关文章:

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 基于DSP的高速便携红外气体分析仪(05-18)

- 嵌入式编程需注意的Cache机制及其原理(05-25)

- 基于DSP的高速数据采集系统设计方案(06-25)

- DSP在无线传感系统中的应用(01-12)