����PCI���ߵ�MPEG-1ѹ������Ӳ����Ƽ�ʵ��

�������ż������������ý�������ͨ�ż����ĸ��ٷ�չ����������ˮƽ����ߣ��Լ������Ƶ�������Ӧ��Խ��Խ�࣬����Ƶ��ء���Ƶ���顢������Ӿ��ȡ��������Ƶ�ṩ���˵���Ϣ�ܶ࣬������Ƶ���������ܴ����ڴ���ʹ洢��ʹ��Ӧ���ܵ��������ơ�Ϊ�����Ƶ���ݵĴ洢�ʹ��䣬Ψһ;�����Ƕ���Ƶ���ݽ���ѹ����

����Ŀǰ��������Ƶѹ��������MPEG-1��MPEG-2��MPEG-4��H.261��H.263�ȡ�����ѹ�������ij���Ⱥ�ѹ��������Ҫ��;�����IJ���MPEG-1��Ϊѹ�����������˻���PCI���ߵ�MPEG-Iѹ�������ÿ���������Ƶ��ء���Ƶ����ȶ���Ӧ�ó��ϡ��ÿ�����һ̨����������ͷ�������ɹ���һ����������Ƶ�ɼ�ѹ��ϵͳ��

����1 ϵͳ�ص�

����(1)֧��BNC��RCA��S-VIDEO��Ƶ�ӿ�;

����(2)֧��PAL��NTSC��ʽ;

����(3)�ɶ���ƵʵʱԤ�������ֱ��ʿɴ�720��576��32;

����(4)�ɶ���������ͬ������;

����(5)�ɶ�������Ƶ�źŽ���MPEG-Iѹ��������MPEG�ļ���VCD�ļ�;

����(6)�û��ɱ��MPEG-1�������ã���֧��CBR��VBR;

����(7)��һ���ͬʱ����;

����(8)�ɴӶ�̬Ӱ���в���֡������JPG��BMP�ļ�;

����(9)֧��Win98/Win2000��

����2 ϵͳӲ�����

����2.1 ϵͳ���

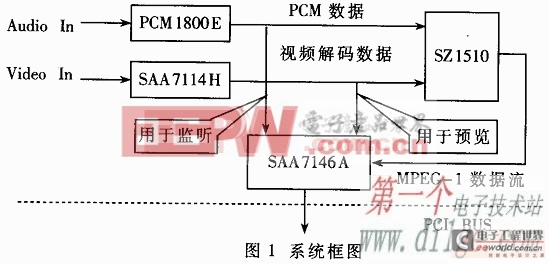

������ϵͳ��Ҫ����Ƶ���롢��Ƶ���롢ѹ�����ĺ�PCI�ӿڵ���ɣ��������ͼ��ͼ1��ʾ��

����2.2 ��Ƶ�������

������Ƶ���벿����Ҫ���ģ����Ƶ��������Ƶ�Ĵ������Թ�����Ԥ����ѹ���á���Ƶ����оƬ���õ���SAA7110��SAA7113��SAA7114�ȡ��������в���Philips��˾��SAA7114��SAA7114����·ģ�����룬����ģ��Դѡ�����ɹ���6��CVBS��2��Y/C��2��CVBS��1��Y/C��4 ��CVBS;��·ģ��Ԥ����ͨ�������п�����˲���;CVBS��Y/Cͨ������ȫ�ɱ�̾�̬������ƻ��Զ�������ƹ��ܣ���CVBS��Y/Cͨ���ɽ����Զ�ǯλ����;���Զ����50Hz/60Hz��Ƶ�������Զ���PAL��NTSC��ʽ�����л�;�ܽ�PAL��NTSC��SECAM�źŽ��뼰ģ���任�õ�����ITU-601/ITU-656�����ֵ����źš���оƬ��Ŀǰ��Ƶ����оƬ�н�����ƵԴ�Ŀ����Լ���Ƶ����ͼ��������õ�һ�֡���ͨ��I2C�ӿڣ����г�ʼ�����á�

������ϵͳ����Image Port��Ϊ������Ƶ����˿ڣ�������Ƶ��ʽ����ITU-656��AI11(PIN 20)��ΪBNC/RCA����ţ�AI12��AI22��ΪS-VIDEO����š�

����ͼ2 SAA7146A����ͼ

����2.3 ��Ƶ�������

������Ƶ���������һ�����ṩ��SAA7146A�����������ã���һ��������ѹ�������ǵ��ɱ�����ϵͳ����BURR-BROWN��˾��PCM1800E����оƬ��˫������Ƭ������20 λADC����+5V��Դ���磬�����Ϊ95dB(����ֵ)����̬��Χ95dB(����ֵ)����Ƕ��ͨ�˲�����֧�����ֽӿڷ�ʽ���������ݸ�ʽ�������Ƶ��Ϊ32kHz��44.1kHz��48kHz��ѡ��

������ϵͳ���ô�ģʽ��20λI2S���ݸ�ʽ����ʱ����SAA7114�ṩ��

����2.4 MPEG-1ѹ���������

������ϵͳ��MPEG-Iѹ��оƬѡ��ZAPEX��˾��SZ1510����оƬ����TI��TMS320C54x DSP�ںˣ��ܶ�ITU-601/ITU-656���ֵ����źź�PCM��Ƶ������MPEG-1ʵʱѹ���������ɶ�����������Ƶ����������Ƶ������������Ƶ�������ȡ�

������оƬ���27MHz����֧�ֶ��������ӿڣ��ɹ����ڸ��û�Ǹ��á�Intel��Motorola�������ߡ�ͨ������ܽ�HCONFIG��1��0����SysConfig�Ĵ��������ó��������߽ӿ����ͣ�Intel 8051���͵�����/��ַ���õ�8λ���ߡ�Motorola���͵�����/��ַ���õ�8λ���ߡ�Intel 8051���͵ķǸ��õ�8λ�������ߡ�Motorola���͵ķǸ��õ�8λ�������ߡ�Intel 8051���͵ķǸ��õ�16λ�������ߺ�Motorola���͵ķǸ��õ�16λ�������ߡ�֧��I2S�����ӿڡ�

������ϵͳ�в���Intel 8051���͵ķǸ��õ�16λ�������ߡ�

����2.5 PCI�ӿڲ������

������ϵͳ��PCI�ӿ�оƬѡ��SAA7146A����оƬ������ͨ�õ�PCI�ӿ�оƬ������һ����ý����(Multimedia Bridge)������ͼ��ͼ2����оƬ����PCI2.1�淶�����а˸�DMAͨ����������Ƶ���ĸ���Ƶ��һ��DEBI(Data Expansion Bus Interface)����������·��Ƶͨ�����ɶ���Ƶ���ݽ������ţ�һ·��������HPS(High Performace Scaler����������ɴ�1��1024������ɴ�1��256;��һ·�м�����BRS(Binary Ratio Scaler��֧��CIF��QCIF��ʽ��

������Ƶ�ӿ���I2SΪ������ͨ����̿�����֧��MSB-FIRST�IJ�ͬ��ʽ����ͬ��ʱ���ʽ��

������ϵͳ�иò�����Ҫʵ�ֹ������£�

����(1)ͨ��DEBI����SZ1510������MPEG-1���ݣ����䵽�ڴ�;

����(2)ͨ����Ƶ�ӿڣ�����SAA7114�������Ƶ�����źţ����������ȡ�ɫ�ȡ����ͶȵĿ��ƣ���ʵ�������Ź��ܢ�ʵ����ƵԤ������;

����(3)ͨ����Ƶ�ӿڣ�����PCM1800E�����PCM�����źţ����䵽�ڴ棬ʵ��������������;

(4)�ṩ����PCI2.1�淶�Ľӿڣ�������