DSP接口效率的分析与提高

2总线不兼容的情况

有一类芯片的总线接口是分时复用的,如CAN总线控制器SJA1000。SJA1000有8位的数据和地址复用的总线,可以和多种MCU直接相连。一次总线操作开始时,总线先传递此次操作访问的地址,在ALE信号将地址锁存后,再进行数据读写。而DSP的数据总线和地址总线被并行地引出,这种并行结构比分时复用的串行结构先进,有着高一倍的带宽。但DSP被设计时并没有考虑过会在芯片外将并行的总线再串行化,也就没有设计相应的辅助信号来完成这种转换。这使得完全使用硬件方法进行串行转换比较困难。此类问题通常使用软件和硬件配合解决,并不真正地靠硬件进行转换,而是把一次总线操作分解成两步。先把此次操作的目标地址作为数据送到总线上,同时通过硬件产生一个锁存信号将其锁存。然后再进行读写操作,读写操作的目标地址就是上一步被锁存的地址。

使用这种办法,硬件和软件都不需要进行复杂的变换。唯一的缺点是指令的效率变低了。由于SJA1000的读写周期一般是DSP的指令周期的几倍,一次访问被分解成两次后多消耗的时间不能忽略。还有一个更重要的影响是,这种转换方法在寻址时无法使用DSP的并行寻址功能,必须使用另外的变量独立运算。在多数的CAN总线应用中,这种处理方法不会对系统的整体性能产生太大的影响。但在有的系统中,这种低效是不可容忍的,如由DSP和SJA1000组成的CAN总线网关,它含有多个SJA1000芯片,并且在SJA1000之间需要经常进行数据块的搬移。对于次数频繁并且寻址有规律的操作,利用DSP的并行寻址功能将极大地提高程序的效率。以下程序段可在两个不同网段的SJA1000之间完成一帧消息搬移功能(它在每次操作的同时对下次操作的地址进行并行寻址):Larar0,mlength;取消息的长度

Larar1,#SJA1_A;一个SJA1000中接收邮箱的首地址

Larar2,#SJA2_S;另一个SJA1000中发送邮箱的首地址

Mar*,ar0

Mar*-,ar1

Loop:?;复制一帧消息

Lacl*+,ar2

Sacl*+,ar0

Banzloop?*-,ar1

如果按上述方法改写这段程序,不仅对SJA1000的操作时间要增加一倍,而且每次操作前都要对地址进行运算,使得完成同样功能的程序运行时间要增加到原来的3~4倍。

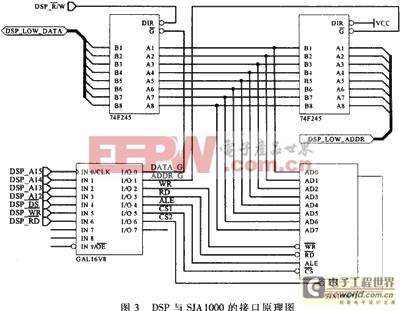

这时,只有使用纯硬件的解决方法才能获得理想的效果。设计的关键是生成合适的锁存信号ALE,使它能够满足SJA1000的时序要求。通过研究DSP控制信号的时序可以发现,从地址建立到读写控制信号有效大约要经历二分之一个CPU时钟的时间,而SJA1000的ALE信号要求的最小宽度为8ns,因此对于主频在50MHz(CPU时钟为20ns)以下的DSP,可以利用这二分之一个CPU时钟的时间间隙生成ALE信号。图3给出了含两片SJA1000的接口电路图。除了片选信号外,这两片SJA1000的总线和其它控制信号都连在一起。假设SJA1000的片选地址为0X8xxx和0X9xxx,各引脚定义与图中对应,则GAL中的逻辑关系如下:

/ADDR_G=DSP_RD*DSP_WR*RD*WR

/DATA_G=/DSP_DS*DSP_A15*/DSP_A14*/DSP_A13*ADDR_G

/WR=/DSP_WR*/ALE

/RD=/DSP_RD*/ALE

ALE=/DSP_DS*DSP_A15*/DSP_A14*/DSP_A13*DSP_RD*DSP_WR

/CS1=/DSP_DS*DSP_A15*/DSP_A14*/DSP_A13*

?/DSP_A12*ADDR_G

/CS2=/DSP_DS*DSP_A15*/DSP_A14*/DSP_A13*

?DSP_A12*ADDR_G

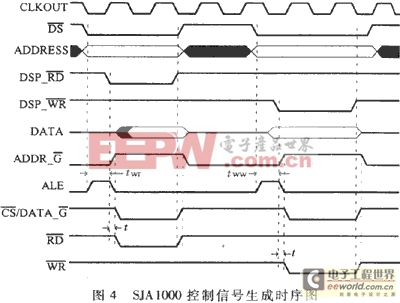

对其中一片进行读写操作,则时序关系如图4所示。

其中,twr、tww分别为DSP读、写时的ALE信号宽度,它们都接近1/2个CLKOUT的周期。t为ALE的下降沿到RD、WR有效的时间,它由GAL翻转的延时产生,为10ns以上(注:本图中DSP的时序来自TMS320C24xxA系列,不同系列的DSP产品之间时序可能有细微的差别)。对于主频高于50MHz的DSP,应当使用有更高工作频率的可编程逻辑器件,并将前面介绍的计数器引入可编程逻辑器件内,来产生满足时序要求的锁存信号。

本文介绍的两种高效率的DSP接口的设计方法,去掉了在DSP访问外设时任何不必要的时间消耗。当然

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)