TI 多内核 DSP 助力航空电子与雷达系统翱翔腾飞

介绍

当今复杂的雷达与航空电子系统要求高处理性能,但同时又面临着小尺寸、轻重量与低功耗 (SWaP) 限制。驱动这些系统的功能都属于信号处理密集型,因此高效实施在高性能低功耗小型处理器上执行的数字信号处理 (DSP) 算法,能够为它们带来极大的优势。此外,这些系统还具有不断提高的设计与数据使用需求。为了满足 SWaP 的效率与自适用性需求,可编程 DSP 与片上系统 (SoC) 现已成为处理平台理想选择。它们能以极低的功耗为雷达与航空电子设备,以及雷达与航空电子常配套的软件定义无线电 (SDR)、影像以及视频应用提供无与伦比的信号处理功能。

要满足对 SWaP 高效率 SoC 不断增长的需求并非易事。这要求既要低成本地提供高性能,又要达到低功耗目的,以实现工作与环保目标。德州仪器 (TI) 基于 KeyStone 的多内核器件是实现 SWaP 效率的关键。它们可为 TI 领先 TMS320C66x DSP 内核进行多内核实施,以小型封装提供每瓦最低功耗。KeyStone 器件以不同的性能提供,在整个系列产品中实现了软件兼容。这可满足多样化需求,在设计时为未来发展预留空间,实现高效开发。

KeyStone 平台中的 TI TMS320C6657 与 TMS320C6655 器件是雷达与航空电子系统的理想选择。这些器件分别为引脚兼容型单内核与双内核 KeyStone DSP。

定点与浮点处理

使用多个数字信号处理器 (DSP) 内核是通过日益复杂的信号处理技术推动波形密集型应用发展的重要技术,可充分满足航空电子设备、雷达、声纳、信号智能 (SIGINT)、影像与视频处理以及软件定义无线电的需求。多内核功能将各种不断丰富的 AccelerationPac 与面向多内核 DSP 的开发工具进行完美结合,能够以紧凑的封装在极低的单位功耗性能下实现高性能。

航空电子、雷达以及相关应用需要多内核 DSP 来满足这些任务关键型应用不断提高的要求,包括更高的处理吞吐量、更精细的分辨率、更高的精度以及高级 I/O 的集成。许多这些功能都依靠浮点数学运算来获得所需的精度。TI KeyStone 架构能够逐指令地在单个器件内提供浮点或定点执行功能,可为设计人员带来高度的设计灵活性。浮点运算执行的时钟速率高达 1.25 GHz,这一速率通常只有定点器件才能达到。设计人员再也不必为获得浮点精度而牺牲性能,或采用分离式定点处理器和浮点处理器进行设计。

主要特性

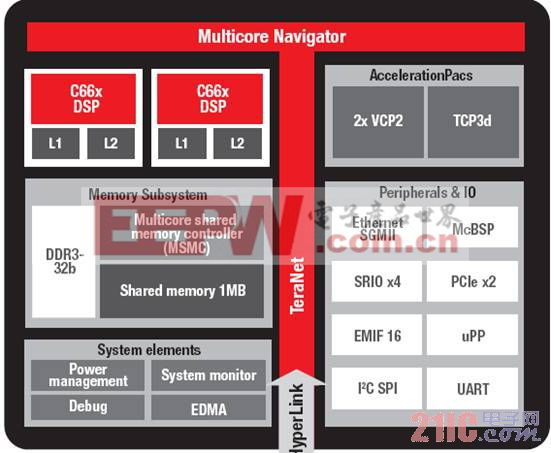

l 基于 TI KeyStone 多内核架构,可实现出众的可扩展性与移植性 | l 完整的多内核共享存储器控制器 (MSMC) |

l 采用单个或两个 TMS320C66x DSP 内核 | l C66x 内核共享的 1MB 低时延 SRAM |

l 40 GFLOP/80 GMAC 的处理功能 | l TeraNet 片上网络互连可实现完整的多内核优势 |

l 在每个内核上进行定浮点运算 | l 多内核导航器为多内核 SoC 软件设计带来单内核设计的便捷性 |

l 定点速度下的浮点性能 | l 高性能 40 纳米工艺技术可提高成本效益 |

l 在 850MHz 至 1.25GHz 下的低功耗 | l 工业温度范围:-40°C 至 100°C 以及 -55°C 至 100°C |

l 业界领先的功耗/性能比 | l 完整的维特比与Turbo AccelerationPac 可提高通信应用 |

AccelerationPac

除优异的 DSP 性能外,C6657/55 还具有维特比及Turbo AccelerationPac,在充分利用每个内核 1MB L2 存储器与 1MB 共享存储器的同时,还可在低功耗硬件中处理通信与波形算法。这些 AccelerationPac 可独立于可编程内核运行,将 DSP 资源释放出来用于其它处理,从而可降低时延,优化软件开发。KeyStone 架构的多内核导航器提供一个基于硬件的抽象层,可将软件开发人员从底层硬件设计的具体繁琐工作中解放出来。多内核导航器的队列与描述符可用于自动将软件任务指向适当的资源,使可扩展性与资源池化成为处理器的整体功能。使用多内核导航器的软件可运行在任何 KeyStone 器件上,无需变更便可提供从一个 DSP 内核到多个 DSP 内核的可扩展性。这些因素综合在一起,可提供以 SWaP 为导向的应用所需的低功耗高性能。C6657/55 采用 40 纳米工艺技术,可在 1.25GHz 的频率下提供高达 80GMAC 和/或 40GFLOP 的性能。图 1 是 C6657 的功能图。

图1:TMS320C6657/55 方框图

高性能 I/O

一般情况下,这些系统不但需要与来自多个厂商的设备进行互操作,而且还要与其它原有系统进行互操作。C6657/55 提供高性能外设集,支持现代系统所需的高数据传输速率,并具有支持原有设计的高灵活性。这些外设包括:

l 双通道 PCI Express 端口,支持每通道高达 5GBaud 的 GEN2;

l 4 通道 Serial RapidIO® (SRIO),符合 RapidIO 2.1 规范,支持每通道高达 5Gbps 的运行;

l 支持与其它 KeyStone 架构器

雷达 系统 翱翔 腾飞 电子 航空 内核 DSP 助力 TI 相关文章:

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)

- 基于DSP和CPLD的宽带信号源的设计(07-26)

- 基于DSP的宽带雷达多片流水分段脉压处理平台设计(08-02)

- 基于MSP430单片机的超声波倒车雷达监测报警系统设计(08-14)

- 基于DSP芯片TMS320的雷达式生命探测仪(10-03)

- 基于FPGA与DSP的雷达高速数据采集系统(02-18)