RS485总线在智能供电系统中的应用

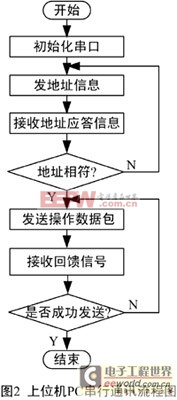

把有效数据做累加,然后与接收到的累加和(即校验码)比较,若相同,则执行相应的操作,并发送成功回馈信息给上位机;若不相同,则说明发送的数据中有错误,将接收数据缓存区清零,并要求上位机重新发送。 3.2PC上位机软件设计 系统上位机程序采用DELPHI语言编写,它具有功能强大、简便易用和代码执行速度快的特点,是新一代可视化快速应用开发工具。利用DELPHI实现串口通信常用的方法有3种:(1)利用控件,如SPCOMM控件、MSCOMM控件及APRO控件等;(2)使用API函数;(3)调用其他串口通信程序。本系统选用较简单的SPCOMM控件来完成串口选择、波特率设置、帧格式设置、发送和接收缓冲区控制、打开串口等任务,用Timer控件控制发送地址码信息。上位机PC串行通讯流程图如图2所示,其串口通信部分相关程序如下: procedureTform1.Timer1Timer(Sender:TObject); begin comm1.BaudRate:=9600;comm1.parity:=None; comm1.StopBits:=_1;comm1.ByteSize:=_8; oper_comm:=true;//串口接受数据流控制变量 comm1.WriteCommData(@sendbuf,1); end; 接收程序代码: procedureTform1.Comm1ReceiveData(Buffer:Pointer;BufferLength:Word); Begin move(buffer︿,(@rbuf)︿,bufferlength);//将缓冲区数据转移到rbuf变量 ifoper_comm=truethen begin 判断接受到下位机发送的应答信息,若是则继续执行 sendbuf:=操作命令字符;//发送操作命令 comm1.writecommdata(@sendbuf,1); oper_comm.:=false; end; elsebegin 接收上传数据并求和校验收到数据 end; End; 3.3DSP下位机串行通信软件设计 下位机DSP串行通信的软件设计可采用查询和中断两种方式,设计中采用了中断方式接收数据、查询方式发送数据。程序分为主程序和中断接收服务程序、发送数据程序3个模块。在主程序中对SCI异步串口进行初始化(包括操作模式、波特率、字符长度、奇偶校验位、停止位位数、中断优先级和使能控制等信息)。需要注意的是,为了保证通信的稳定可靠,串行通信控制寄存器SCICTL1的休眠位SLEEP设置很重要,具体方法为:初始化时将所有下位机DSP的SLEEP位都设成1,使得它们在仅当检测到地址字节时才被中断,在中断服务程序里,将接收的地址与本机地址比对,若相同,则软件清除SLEEP位以确保SCI在接收到每一数据帧都产生中断,否则SLEEP位仍保持以1,以接收下一个地址帧。DSP接收数据中断流程图如图3所示。 本文介绍了公寓智能用电管理系统中利用RS485总线实现PC机和多台DSP的远程串行通信设计方案。实践证明,该设计运行可靠,抗干扰性强、可完成较长距离的串行数据通信任务。该方案对其它基于DSP的远程数据通信设计具有一定的参考价值。 本文的创新点是,利用DSP内部的专用串行通信模块SCI及RS485专用接口芯片MAX485实现了PC机与多台DSP的通信,大大减少了系统的外围设计,通过正确设置SCI中串行通信控制寄存器SCICTL1的休眠位SLEEP,避免了通信混乱,提高了总线抗串扰的能力。 参考文献 [1]刘和平,王维俊等著.TMS320LF240xDSPC语言开发应用[M].北京:北京航空航天大学出版社,2003. [2]江思敏等著.TMS320LF240xDSP硬件开发教程[M].北京:机械工业出版社,2003.6. [3]张磊,陈建锋,全力.DSP控制的开关磁阻电机系统远程数据通信的研究.中小型电机,2005,32(2):43-46 [4]王炼红,章兢.TMS320F2812DSP与PC机的串口通信设计.微计算机信息,2006,07Z:173-175

4结束语

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)