基于高速串行BCD码除法的数字频率计的设计

数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。采用VDHL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分以外,其余全部在一片FPGA芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。在不更改硬件电路的基础上,对系统进行各种改进还可以进一步提高系统的性能。该数字频率计具有高速、精确、可靠、抗干扰性强和现场可编程等优点。

在设计中,所有频段均采用直接测频法对信号频率进行测量,克服了逼近式换挡速度慢的缺点;采用了门控信号和被测信号对计数器的使能端进行双重控制,提高了测量的精确度;在运算单元采用了高速串行BCD码除法,不仅提高了运算速度,而且减小了资源消耗。

1 系统结构及基本设计原理

以一个8位十进制、测量范围为1Hz~100MHz的数字频率计为例,采用100MHz的标准频率信号,说明设计的基本原理及实现。设计的数字频率计由测量频率模块、计算模块和译码模块组成,如图1所示。测频模块采用两个十进制计数器分别测出门控时间内的标准信号和被测信号的周期数Ns和Nx。计算模块则根据公式Fx/Nx=Fs/Ns算出Fx,通过译码即可得到被测信号频率的7段数码显示。

数字频率计的设计原理实际上是测量单位时间内的周期数。这种方法免去了实测以前的预测,同时节省了划分频段的时间,克服了原来高频段采用测频模式而低频段采用测周期模式的测量方法存在换挡速度慢的缺点。

为克服低频段测量的不准确问题,采用门控信号和被测信号对计数器的使能信号进行双重控制,大大提高了准确度,如图2所示。

当门控信号为1时,使能信号并不为1,只有被测信号的上升沿到来时,使能端才开始发送有效信号,两个计数器同时开始计数。当门控信号变为0时,使能信号并不是立即改变,而是当被测信号的下一个上升沿到来时才变为0,计数器停止计数。因此测量的误差最多为一个标准时钟周期。当采用100MHz的信号作为标准信号时,误差最大为0.01μs。

2 高速串行BCD码除法运算原理

利用FPGA实现二进制除法运算,一种方法是采用逼近法,这种方法速度低、准确性不高。另一种方法是采取被除数与除数的倒数相乘的方法,即将除数作为寄存器的地址,其倒数的小数部分作为寄存器的内容,通过一次寄存器寻址来计算除数的倒数。这种方法在一个时钟周期内即可完成一个完整的除法运算,虽然速度较高,但对于多字节除法运算,不仅程序复杂,而且占用资源较多。根据频率计的实际情况,本设计采用串行除法运算,利用多个时钟周期完成一个完整的除法运算,从而兼顾了频率计对速度和资源两方面的要求。

2.1 多位串行BCD码减法原理

在数字串行除法运算中,减法运算是必不可少的部分。数字串行BCD码的减法运算是将P位的BCD码分为P个宽为4的二进制数,然后从低位开始相减,在P个时钟周期内完成减法操作。如果输入的操作数位数为8,那么串行BCD码减法器可以在8个时钟周期内完成8位BCD码减法运算。

数字串行减法的控制也比较简单,1位BCD码减法运算完成,进行移位操作,并且移位次数加1,然后通过采用start信号指示新计算周期。当移位次数为n时,输出移位寄存器完成串/并转换,输出结果。设计者可以根据实际情况,通过选择不同的n,提高设计的灵活性。本设计选择n=8。

该设计在提高速度的同时,节省了资源。实验证明,采用1OOMHz的工作频率,实现一个8位BCD码串行减法运算,耗用的资源却小于实现2位BCD码并行减法运算所耗用的资源。

2.2 多位串行BCD码除法原理

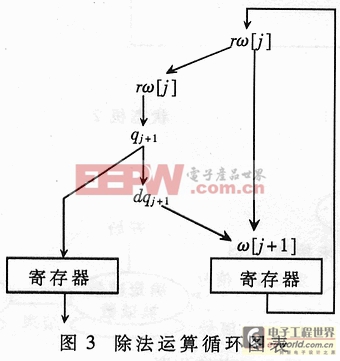

本设计采用循环式除法运算,循环原理可以用下面的公式表示[1]:

ω[j+1]=rω[j]-dqj+1

式中,ω[j]为第j步的余数,ω[0]为被除数;d为除数;qj+1为第j+1步所得的商;r为与移位步长有关的常数,在此取为16。

除法运算循环图表如图3所示。

循环步骤如下:

·将ω[j]左移四位,构成rω[j]。

·通过多次BCD码减法运算,求得部分商qJ+1,得到部分余数。

·部分余数、部分商移位,准备下次循环。

高速串行BCD码除法是建立在BCD码减法运算基础上的循环运算。用被除数减除数得到部分余数的BCD码,如果够减,则使商加1;否则,余数和商同时左移四位,并记录移位的次数m,根据对有效位数的不同要求,可以对m进行赋值,如果要求保留8位有效数字,则m=8。

在这种循环除法运算中,减少循环的次数是提高运算速度比较有效的方法。在一般循环式除法运算中,是从低位开始进行循环相减,循环次数等于商。如果是8位除法运行,则得到一个8位的商,要进行8位次的BCD码减法循环,例

- TMS320F28335在电网频率测量中的应用(10-25)

- 基于FPGA的等精度频率计IP Core设计(06-05)

- 一种于FPGA的多通道频率测量系统设计(08-12)

- 单片机与FPGA实现等精度频率测量和IDDS技术设计方案(07-02)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)