一种于FPGA的多通道频率测量系统设计

摘要:设计了一种多通道频率测量系统。系统由模拟开关、信号调理电路、FPGA、总线驱动电路构成,实现对频率信号的分压、放大、滤波、比较、测量,具备回路自测试功能,可与主设备进行数据交互,具有精度高、可扩展、易维护的特点,有一定的工程应用价值。

频率测量电路是很多检测与控制系统的重要组成部分,在航空机载计算机领域具有广泛的应用环境。随着检测与控制系统复杂程度的提高,频率测量电路也被提出了新的要求,例如多通道实时采集、高精度测量等。FPGA的特点是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写,因此,以FPGA为核心进行电路搭建已成为当前数字系统设计的主流方法。本文利用FPGA设计了一种多通道频率测量系统,易于扩展,精度较高,符合实际的需求。

1 系统硬件设计

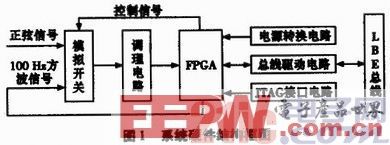

系统硬件由模拟开关、信号调理电路、FPGA及其外围电路、总线驱动电路构成。

模拟开关完成对频率信号输入通道的切换,当系统处于正常工作状态时,外部输入的正弦信号经模拟开关进入后级电路,进行频率测量;当系统处于自测试状态时,由FPGA产生一个频率恒定的方波信号,该信号经模拟开关进入后级电路进行频率测量,通过对比设定频率和测量频率的一致性来监测整个系统是否存在故障点。

信号调理电路完成对正弦信号的前级处理,设计准则是满足全频段信号的调理需求,分以下几级电路:1)使用3个阻值相同的电阻对正弦信号进行1/3分压,防止高频信号的幅值超过放大器及比较器的输入电压阈值;2)使用仪表放大器对正弦信号进行放大,原因是低频信号的幅值低于比较电压,如果不进行放大就不具备比较意义,而且放大器具有输出电压饱和特性,不会造成放大器的输出电压超过比较器的输入电压阈值;3)使用运算放大器及分立的阻容对正弦信号进行二阶RC滤波;4)使用比较器将正弦信号转换成方波信号,供FPGA采集。

FPGA及其外围电路是整个测量系统的核心。外围电路包括以下几个部分:1)电源转换电路,将5V电源转换为FPGA工作必需的3.3 V及2.5 V电源;2)程序存储器电路,负责存储可执行逻辑代码,供FPGA工作时调用;3)JTAG接口电路,方便开发者进行可编程逻辑的烧写和调试。FPGA主要完成以下几个功能:1)产生1路用于系统自测试的幅值为3.3 V、频率为100 Hz的方波信号;2)进行逻辑译码,根据总线指令控制模拟开关及总线驱动芯片的动作;3)对输入信号进行数字滤波,测量信号频率,并将计算结果送到数据总线上供主设备采集。

总线驱动电路是测量系统与主设备进行数据交互的桥梁,完成FPGA电平与LBE总线电平之间的相互转换,并配合读写时序控制数据的流通方向。当测量系统不需要与主设备进行通信时,关闭输出使能开关,保证测量系统的数据不会干扰到总线数据。

系统硬件结构框图如图1所示。

2 可编程逻辑设计

2.1 测频公式

测量频率的方法主要有两种:

1)测频法。在给定时间T(N个基准信号f0)内对被测信号进行周期计数,计数值为M,则被测信号的频率为:

由于计数器只能计整数,所以误差由△M=±1引起,计算结果的误差为:

由式(2)可以看出,在时间T一定的情况下,频率越高,相对误差越小。

2)测周法。在被测信号一个周期内对基准脉冲f0计数,计数值为M,则被测信号的频率为:

由于计数器只能计整数,所以误差由△M=±1引起,计算结果的误差为:

由式(4)可以看出,在基准脉冲f0一定的情况下,频率越低,相对误差越小。

综上所述,测频法比较适合高频信号,测周法比较适合低频信号。本系统测量的正弦信号频率范围为20~3 300 Hz,为了提高测量精度,选用测周法的思想设计可编程逻辑电路。

2.2 可编程逻辑设计

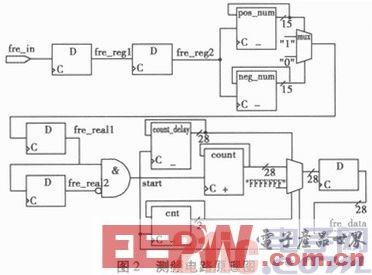

可编程逻辑采用模块化的设计思想,根据不同数量的通道需求,重复“调用”测频模块,配置逻辑电路,便于进行功能扩展。测频电路的原理如图2所示,图中带有“D”字样的功能块表示D触发器,带有“mux”字样的功能块表示多路选择器,带有“count”或“cnt”字样的功能块表示计数器。

频率测量的过程主要分为四个步骤:输入信号同步、数字滤波、频率计数、计数值输出。

1)由于输入被测频率信号fre_in为异步信号,因此需要经过两级同步器对其进行同步处理,得到同步后的频率信号fre_reg1、fre_ reg2。

2)由于系统时钟频率为33 MHz,被测频率信号的频率相对较低,为了减少毛刺对频率测量的影响,同时达到系统要求的可测频率范围,可对同步后的频率信号进行滤波处理,其上限截止频率设为3 300

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)