工程师分析实例,带你走近Xilinx FPGA设计

一.概述

本文主要帮助大家熟悉利用ISE进行Xilinx 公司FPGA 代码开发的基本流程。主要是帮助初学者了解和初步掌握 ISE 的使用,不需要 FPGA 的开发基础,所以对每个步骤并不进行深入的讨论。

本文介绍的内容从新建 project 一直到下载到硬件观察现象为止,涵盖整个开发过程。考虑到我们的开发一般以 Verilog HDL 或 VHDL 为主,在本文中未介绍原理图输入工具和 IP 核使用工具等。这同时是出于为了使文章脉络更清晰,让大家更快地学会 ISE 的考虑。关于这些专用工具,可以参看 HELP 或者其他文档。

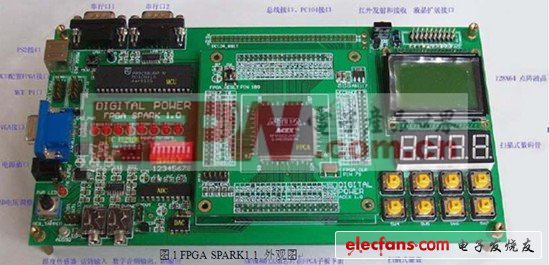

为了更直观的理解,我们需要一个实验平台,在本文中,采用的是 Digital Power Studio 工作组 FPGA SPARK1.1 综合开发平台的 Xilinx 标准型开发系统。如图 1 所示(图中为 Altera 子板,只需改成 Xilinx 的即可)。在该开发系统中,所采用的芯片是SPARTANII系列的XC2S200 。

图1 FPGA SPARK1.1 外观图

二.实现功能

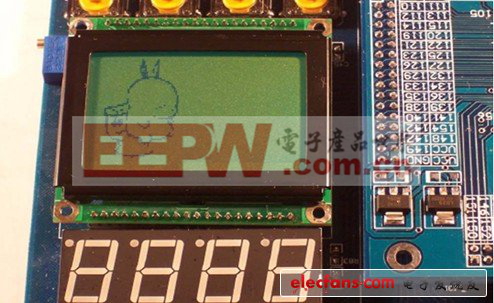

在如上系统中右边有一个 128×64 带背光的点阵型液晶。我们的实验就是用Verilog HDL 编写一段代码驱动液晶显示一个流氓兔。其效果如图 2 所示:

图2 点阵液晶上显示流氓兔的效果图

三.软件准备

本文介绍的是 Xilinx 公司的 ISE 开发环境。现在最新的版本是 ISE7.1,其界与 ISE5.x/ISE6.x 一致。为了更好地进行仿真,还需要安装 Modsim。但是 ISE本身可以进行仿真,也可以不安装 Modsim。流程介绍:

1.新建项目

在开始—〉程序—〉Xilinx ISE 中找到 Project Navigator,点击打开。也可以通过双击桌面上 Project Navigator 的快捷方式打开。ISE 开发环境如图 3 所示:

图3 ISE 开发环境

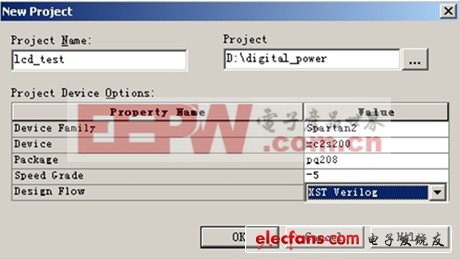

图3 中选择 File—〉New Project,进入图 4;

图4 新建 project 界面

在 Project Name 栏输入项目名称,Project 中填入该项目的目录,Project Device Options 中,Device Family 为所用芯片所在系列,Device 为所用芯片,Package为所用芯片的封装形式(每个芯片可能有不同封装的几种,如 XC2S200 有 3 种封装的),Speed Grade 为速度等级,Design Flow 为所选用综合方式(综合工具

和代码语言)。由于采用的是 FPGA SPARK1.1,采用如图 5 的设置。

图5 新建项目的信息输入

其中 XST Verilog 表示采用 ISE 自带的综合器,代码语言为 Verilog HDL,ISE支持其他综合工具的调用,也支持标准 edif 文件的输入。XST 是 ISE 自带的综合工具,由于 Xilinx 对自身的硬件了解程度比任何第三方软件开发商都更深,故XST 的综合性能有自身独特的优点。

点击 ok,新建项目完成。可以在相应目录下看到生成的文件。效果如图 6。如果要更改硬件的设置,可以双击图 6 中模块视窗内蓝色选中的所示对应选单,即可进入 project properties 界面重新进行设置。

图6 效果图2.编写和导入代码文件

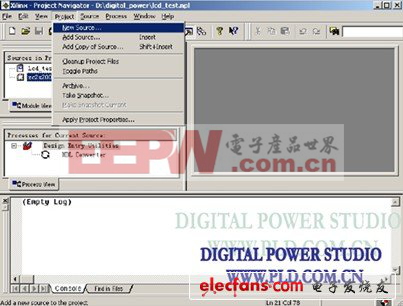

如图 7 中所示,在 Project 菜单下,选择 New Source 建立新的代码文件。弹出的对话框如图 8 所示。

图7 Project 菜单

图8 新建代码文件对话框

在 File 中输入文件名称,Location 最好选用和 project 文件所在目录同一个目录。将 Add to project 选单选中,该文件将自动被加入当前 project 中。在左边窗口中选择建立的文件类型,如图 8 选为 Verilog Module。点击下一步,如图 9所示。

图9 Verilog 代码文件定义对话框

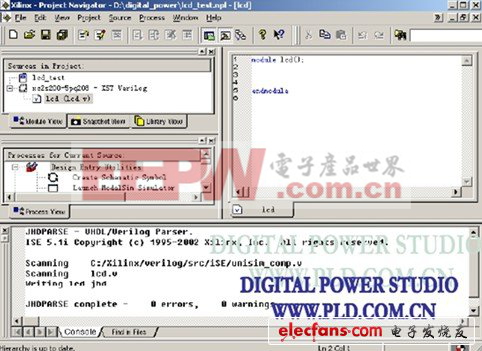

在图 9 中,可以定义代码文件的输入输出端口,可以不进行定义,直接点击下一步。如果进行了定义的话,生成的代码文本文件会自动加上定义好的输入输出端口。点击下一步,进入下一对话框后点击完成,即可。如图 10 所示。在图10 中,可见左面 Module View 中 project 中已经多处了刚才建立的 lcd 模块,右边打开的 lcd 文件界面中,可以进行代码的编写。

图10 代码文件生成后界面

前面介绍的是编写代码,如果已经用其它工具编写好了代码,或者有现成的代码,则不需要再重新编写了,下面介绍如何将已有的 verilog 文件导入到 project中。

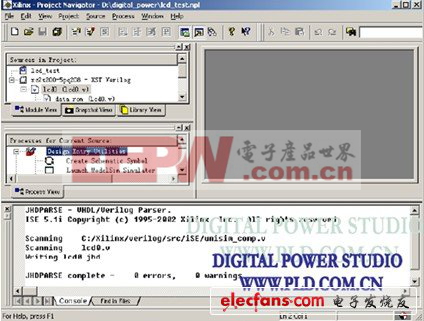

在图 7 中不要选择 New Source,而选择 Add Source。在弹出的窗口中找到已有代码文件(可同时加多个文件),并点击“打开”即可。注意:Add Source 是将当前选择的代码加入到当前 project 中,而 Add Copy of Source 是将代码文件复制到当前 project 所在目录中,并将复制后的文件加到 project 中。建议使用后者。添加后结果如图 11 所示。(在本文例子中,加入的是 Digital Power 提供的液晶程序 lcd.v。)可以看到在Module View 窗口中将显示出 verilog 代码中所有Module,并显示出其层次结构以及其所在的文件。

图11 Add Source 结果图

FPGA 设计 Xilinx 走近 分析 实例 工程师 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)