FPGA时序收敛分析

时间:08-01

来源:互联网

点击:

时序约束的重要性

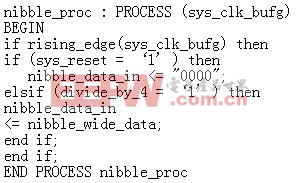

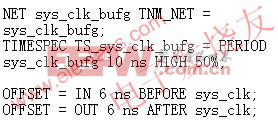

如果您希望自己的逻辑正确运行,则必须采用正确的时序约束。如果您已经慎重确保代码全部同步且注册了全部 I/O,则这些步骤可以显著简化时序收敛。在采用上述代码并且假定系统时钟为100MHz 时,则只需四行代码就可以轻松完成时序约束文件,如下所示:

请注意:赛灵思 FPGA 中 I/O 注册逻辑的建立与保持时间具有很高的固定性,在一个封装中切勿有太大更改。但是,我们仍然采用它们,主要用作可确保设计符合其系统参数的验证步骤。

三步简单操作

仅需遵循以下三步简单操作,设计人员即可轻松实施可靠的代码。

• 切勿让综合工具猜测您的预期。采用赛灵思原语对所有 I/O 引脚和关键逻辑进行明确定义。确保定义 I/O 引脚的电气特性;

• 确保逻辑 100% 同步,并且让所有逻辑参考主时钟域;

• 应用时序约束确保时序收敛。

只要遵循上述三个步骤,您就能够消除综合与时序导致的差异。扫除这两个主要障碍会让您获得具有 100% 可靠性的代码。

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 关于Linux操作系统的NTFS和内核分析(05-19)

- Linux 2.4.x内核软中断机制(04-06)

- 基于DSP的人脸识别系统设计(04-26)

- 3D图形芯片的算法原理分析(07-16)

- 解析:视频图像智能分析处理技术(08-08)