用于CMOS图像传感器的流水线ADC设计及其成像验证

CMOS图像传感器(CMOS image sensor,CIS)在近二十年来取得了飞速的发展,得益于有源像素传感器(Active PixelSensor)的出现、相关双采样技术(Correlated Double Sampling)的发明以及工艺的进步等,用于低噪声应用领域的CMOS图像传感器也取得了长足的发展。由于CMOS传感器具有先天的低成本、易于集成等优点,CMOS传感器在低噪声应用领域也已引起了越来越多的关注。目前,在低噪声CMOS图像传感器的研究领域,除研究其噪声外,数字化也是它的一个重要的研究方向。

文中介绍了一种适用于低噪声CMOS图像传感器芯片级模数转换的流水线型ADC,根据低噪声CMOS图像传感器的系统要求,文中设计的ADC的分辨率为12 bit,速度为10 Msps,采用了每级1.5 bit、共11级的流水线型结构。在该ADC完成设计仿真后,基于0.5μm标准CMOS工艺进行了流片。最后在PCB板级电路上用该ADC对一个自主设计的模拟输出的CMOS图像传感器进行了模数转换,并基于自主设计的成像测试系统完成了CMOS图像传感器的成像。

1 ADC设计指标及框架

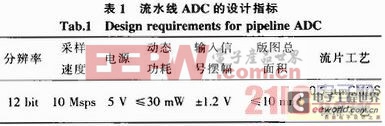

根据自主设计的低噪声CMOS图像传感器的系统要求,可以确定流水线ADC的设计指标。表1给出了该设计的具体设计指标。

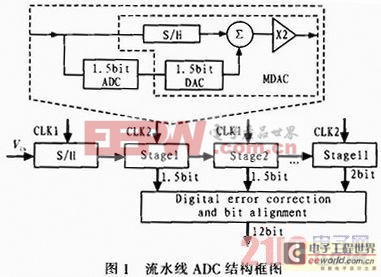

由于该ADC设计目标为应用在自主设计的低噪声CMOS图像传感器的芯片级,因此其速度和精度都应尽可能的高,以达到芯片系统低噪声和速度的要求。而由于其工作在芯片级,其功耗和面积的要求则可以相对宽松一些。因此本设计采用了11级,1.5 bit每级的结构,虽然这种结构在功耗上会有所增加,但是可以降低比较器的比较精度带来的影响,同时也降低了对第一级采样保持电路运放的要求。本文设计的ADC的结构框图如图1所示,在该ADC11级结构中的前10级电路中,每级电路包括子模数转换器(ADC)、子数模转换器(DAC)、求和电路、余量放大器以及采样保持电路,其中由于子DAC、采样保持电路、求和电路以及余量放大电路一般都由一个开关电容电路实现,因此该电路模块常被统称为乘法型数模转换器(Multiplying digital to analog converter,MDAC),第11级电路为一个2 bit的flash ADC。在两组互不相交时钟CLK1和CLK2的控制下,每级电路都产生了数字输出,这些输出在经过数字位对齐和数字校准后得到最终的数字输出。

2 ADC各模块设计

2.1 MDAC设计

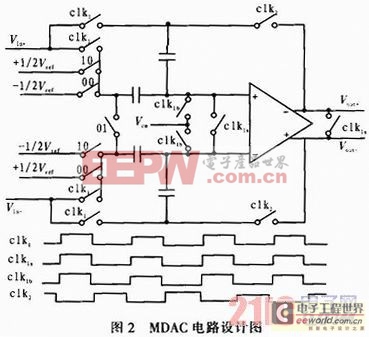

MDAC电路是流水线ADC设计中非常重要的部分,它在ADC中实现的功能包括采样保持、数模转换、减法和余量放大等,一般采用开关电容技术实现,由模拟开关、电容和跨导运算放大器(OTA)构成,其电路图如图2所示。其工作原理是:用MDAC的采样保持对前级余量电压进行采样;将其采样电压与本级子DAC的输出电压进行减法运算;将减法运算得到的余量电压通过余量放大器进行放大。

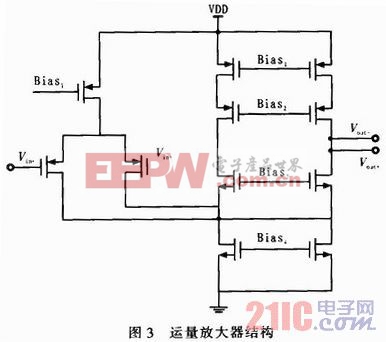

在流水线ADC结构中,第一级的MDAC的要求最高,随着级数的增加,要求不断降低。对于一个12位、10 Msps采样率流水线ADC,以第一级MDAC为例,该电路需满足的总体指标为:精度12 bit,采样率10 Msps。而在MDAC设计中,最关键的是余量放大器设计,本文以第一级余量放大器的设计为例来说明整个设计,其中采用的余量放大器的结构如图3所示。余量放大器工作在闭环状态,要求其有限直流增益造成的误差小于1/2LSB,即有:

式中A0为开环增益,N为ADC分辨率,β为反馈系数。

另外,由于余量放大器有限的带宽,因此对输入电压响应需要经过一定的时间才能趋于稳定。在采样频率为f的ADC中,要求信号在二分之一的时钟周期内达到所需的精度(即误差小于1/2LSB),即有:

式中GBW为单位增益带宽,N为ADC分辨率,β为反馈系数,f为采样频率。

对于本文的ADC设计有:N=12,β=1/2,f=10 MHz,因此由公式(1)和公式(2)可得,用于本文第一级MDAC的余量放大器应满足:开环增益需大于84 dB,单位增益带宽需大于58 MHz。综合考虑到输入信号摆幅、流片工艺和功耗等要求,本文的余量放大器采用了折叠共源共栅的运放结构,仿真结果表示,该结构可满足设计要求。

2.2 比较器设计

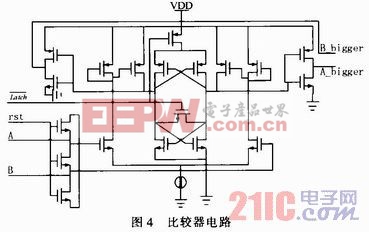

流水线ADC由于采用了校正电路,对比较器失调电压的要求放宽了。对于1.5 bit每级的电路,设参考电压为1 V,则它的失调电压放宽为125 mV。本ADC中从第1级到第10级电路都采用了动态比较器,因为其失调电压小于可校正的最大失调电压,同时它具有较快的速度和较低的功耗。该电路的原理图如图4所示,它包括一个由rst信号控制的快速复位电路、信号输入的预防大电路、锁存比较器以及输出反相器组成。

2.3 数字位时间对齐及数字校准电路设计

由于流水线ADC每级电路产生数字代码的时间不同,因此,在进行数字校正之前,必须先对其进行延迟,所以在数字校正电路之前必须要有数字延迟电路。完整的输出数字时间对齐及数字校正电路如图5所示,其中图的左边为数字位时间对齐电路,图的右边为数字校准电路。

流水线ADC CMOS 图像传感器 Labview 相关文章:

- DSP内嵌PLL中的CMOS压控环形振荡器设计(03-02)

- 基于DSP内嵌PLL中的CMOS压控环形振荡器设计(05-05)

- 宽动态监控摄像机CCD/CMOS-DSP解析 (07-24)

- DSP与单片机通讯方式解析方案 (08-29)

- 基于ATmega162的智能仪器设计(08-18)

- 基于STC单片机的太阳能热水器智能节水控制系统设计(06-02)