40纳米500MHz DSP核心的时钟设计与分析

OR)。

RC分布扩展

RC延时分布是可用以改善设计期间时钟树鲁棒性的第一个指标。时钟树RC延时百分比等于互连线延时在每个接收端(sink)总插入延时中所占比率。

对于每个时钟网路:

%RC delay = [RC delay ]/[RC delay + Gate delay]

窄(10%)分布意味着良好的跨角点时钟延时追踪。互连线在时钟路径占主导地位与门在时钟路径占主导地位相交叠的机率比较小。这种分析不包括数据路径时钟树。

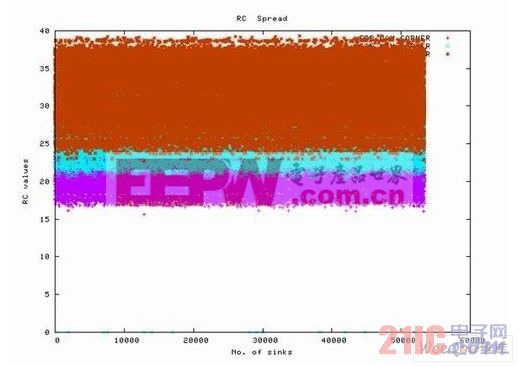

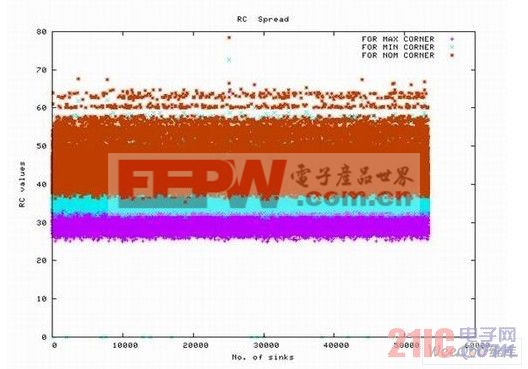

图2显示了一种更好的RC扩展分析 。在图3中,采用了微捷码自带CTS的NOM角点RC扩展率在25%以上,而图2的则在15%左右。在图3中,MAX 角点RC扩展率在10%左右,而图2的则在5%左右。

图 2 使用新时钟设计方法的RC扩展

图3 使用微捷码自带CTS的RC扩展

插入延时扩展

插入延时分布是可用以改善设计期间时钟树鲁棒性的第二个指标。不同角点的插入延时通过使用以下方法实现w.r.t WEAK角点(QC_MAX)标准化。

1) 每个时钟接收端的插入延时是依据不同角点来计算的。称呼延时为,Di,corner

2) 一个角点的插入延时率等于每个接收端插入延时除以WEAK角点插入延时。

Ri,corner = Di,corner/Di,WEAK

3) 上述插入延时率的平均值是针对每个角点来计算。

Avgcorner= ∑iRi,corner/N, 在此N系指接收端的数量

4) 每个接收端的插入延时率等于每个角点平均率的标准值。

NRi,corner=Ri,corner/Avgcorner

5) 现在,{NRi,corner}的划分如图4和图5所示。WEAK角点结构位于y=1这一条直线。

图4显示了一个50ps的较低扩展,这意味着更好的跨角点延时追踪。在图5中,微捷码自带CTS结果显示了超过150ps的较高扩展。

图4使用新时钟设计方法的插入延时扩展

图5使用微捷码自带CTS的插入延时扩展

同级延时扩展

同级延时分布是可用以*估设计期间时钟树鲁棒性的第三个指标。它是通过以下程序进行计算:

1)对于每个接收端,让Di,corner 作为插入延时,让Li 作为时钟树深度。

2) 每个接收端平均级延时为

Si,corner=Di,corner/Li

级被定义为一个缓冲器和其驱动的互连线。

3) 计算所有“平均级延时”的全局平均值,

ESDcorner= ∑iSi,corner/N

4) 计算同级延时,

ESi,corner=Di,corner/ESDcorner

5) 理想上,每个接收端应可跨角点地拥有同等的级数,例如,对于接收端j,

ESj,corner1=ESj,corner2=…

图6和图7所展示的例子是相同级数以及两种实现方式的扩展。在图6中,ESD扩展拥有从18到23的一种更好分布。在图7中,微捷码自带CTS结果显示了从27到37的一种分布。

图6使用新时钟设计方法的 ESD扩展

图7使用微捷码自带CTS的ESD扩展

新时钟设计方法已经实施于40纳米DSP核心。事实证明,使用这种方法的CTS单元门数要比使用微捷码自带CTS工具的少了17%。鲁棒性低偏斜时钟树分布现已成功实现。实验结果显示,新设计方法在降低保持缓冲器门数方面可起到很好效果。同时这种设计方法还可用于H-tree时钟结构。未来工作中,我们还将部署更多分析来改善功耗。

设计 分析 时钟 核心 500MHz DSP 纳米 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)