基于TMS320C6678 DSP的电源设计方案

1 电源硬件电路设计与计算

1.1 系统总体方案设计

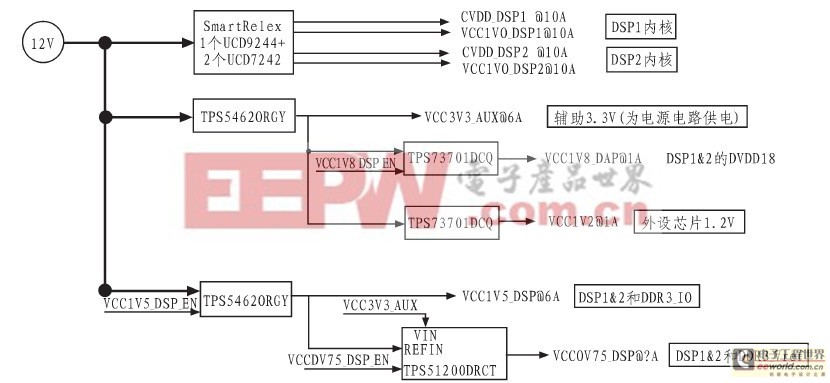

图1是系统的组成框图。采用统一的12 V电源进行供电,DSP的内核电压由一片UCD9244和两片UCD7242组成;经过TPS54620产生的3.3 V电源可以为其他的电源电路供电;大部分的模块电源需要经过滤波网络的处理,这样做可以降低电源的纹波、噪声,同时也可以很好地解决PCB布板带来的其他干扰问题。

图1 系统组成框图

虽然DSP不要求内核电压与IO之间有特殊的上电时序,但假如有某个模块的电源处于错误状态时,得保证整个系统的所有电源都不在工作,否则,会严重影响器件的使用寿命与可靠性。所以,在本设计中,上电时序为CVDD,VCC1V0,VCC1V8,VCC1V5,VCC0V75;其中CVDD与VCC1V0的上电时序通过对UCD9244芯片进行编程实现,其他模块的上电时序通过TPS3808系列芯片,前一级对后一级产生控制信号实现。掉电时序和上电时序完全相反,这样可以防止大量的静态电流和器件过压情况发生。

任何DC/DC变换器在开始设计时,工作频率的选择都是很关键的。它主要取决于3个因素:最大效率,最小尺寸和闭环带宽。工作频率高,通常效率就低,设计尺寸小。综合考虑,在本设计中,选择750 kHz.

在设计的最后,为关键的电源供电部分添加了信号指示灯,若上电正常则可以使LED亮,它在电路中的作用主要是为了方便调试,同时,在电路上电不正常的时候可以马上发现哪个模块出错,从而可以很快地找到原因。

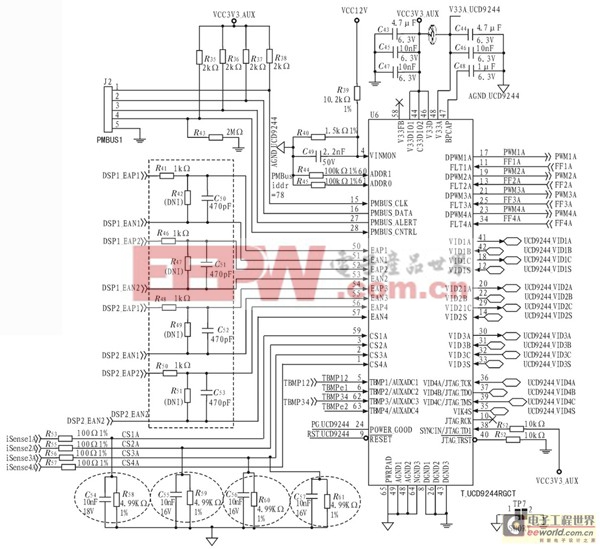

1.2 UCD9244控制电路

UCD9244芯片是数字PWM控制器,能同时控制4路输出,开关频率达到2 MHz,采用PMBus v1.2标准。PMBus是电源管理总线,是从SMBus发展过来的,在数字通信总线上与电源转换器进行交流。图2是UCD9244的控制电路图,输出电压的调节主要有两种方式,一种是通过VID接口,这种方式需要有DSP或者专用集成电路的控制,但本设计中本来就是作为DSP的电源,所以采用另一种调节方式--通过PMBus命令语句,对输出电压幅值进行控制,这种方式也更为简单有效。为保证UCD9244整体工作,在工作电压输入端增加了旁路电容来减少电压纹波,同时也对高温、过流等异常情况增加了保护措施。

图2 UCD9244控制电路图

UCD7242是与UCD9244完全兼容的驱动芯片,可以驱动两个独立的电源,可以供应CVDD(内核电压)与VCC1V0(SRIO、PCIE、SGMII和Hyperlink)。通过1片9244控制两片7242来达到为两片DSP6678供电的目的。UCD7242电路中电感值的选择很关键,根据芯片内部结构,电感值的计算可以通过下面这个公式决定:

式中:VIN为输入电压,VOUT为输出电压,fs为工作频率,D为占空比,△I为电感电流峰峰值。在本设计中,VIN=12 V,VOUT=1 V,D=1/12,fs=750 kHz,△I=10 A,可计算得电感,L≈0.122μH.

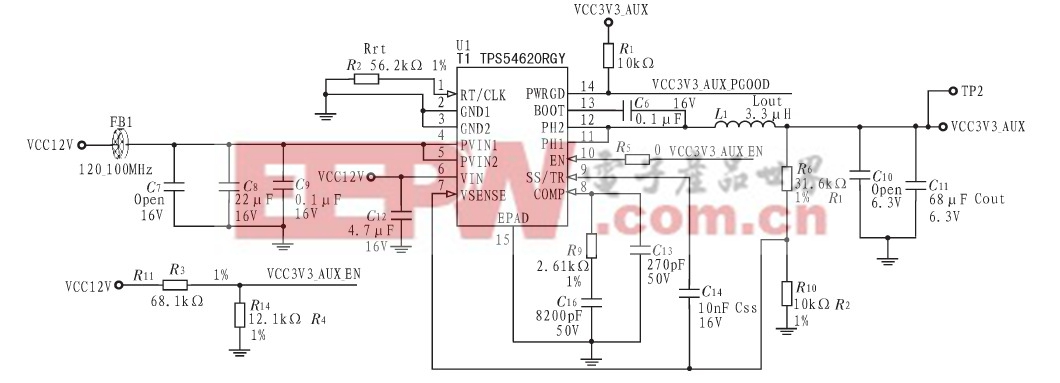

1.3 3.3 V辅助电源电路

在整体的系统中,有些芯片是需要3.3 V的工作电压的,比如TPS73701,为DSP IO供电;TPS51200作为DDR3的参考电压。图3为采用TPS54620芯片作为电压转换芯片的电路,TPS54620的耐热性能增强,功能齐全,支持高效率,集成了高侧/低侧MOSFETs,并且输出电压可以调节。在本设计中,用TPS54620产生了3.3 V和1.5 V的电压。如图3所示,输出电压为:

式中:R10、R11为分压电阻,Vref为参考电压,经实验设定R10=31.6 kΩ;R11=10 kΩ;Vref=0.8 V,可以得出输出电压VO=3.3 V。

图3 3.3 V辅助电源电路

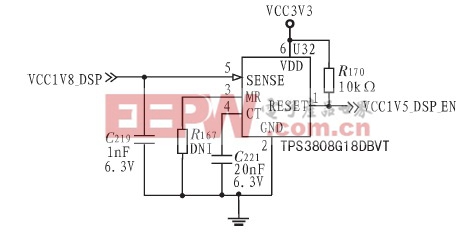

1.4 时序控制电路

该时序控制电路主要是用来控制6678DSP的IO、DDR3参考电压以及HyperLink、PCIE等上电时序的。以DVDD18先于DDR3_IO上电为例,电路原理图如图4所示,所用的芯片为TPS3808G18,只有DVDD18=1.8 V时,RESET才会输出一个高电平,从而可以驱动下一级电路,这样就保证了时序要求,值得注意的是,延迟时间是可以控制的,通过控制CT引脚与地之间的电容值就可以实现,参考公式为:

CT(nF)=[tD(s)-0.5x10-3(s)]×175 (3)

式中tD为设置的延迟时间。

图4 时序控制

1.5 滤波网络

在过去的DSP中,EMI滤波器(T型滤波器)用在那些易受噪声影响的电源轨中,这些滤波器通常都是低通滤波器,这样可以限制在每个相应电源供应的寄生耦合噪声而不至于把直流分量滤除。其实,在设计PCB板的时候,

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)