PCI总线目标控制器的设计

0引言

PCI(PeripheralComponentInterconnect)总线是微型计算机中处理器/存储器与外围控制部件、扩展卡之间的互联接口。PCI总线规范是互联机构的协议,以及电气和机械配置的规范,是当今高性能微型计算机事实上的总线标准。[1]

PCI总线控制器为PCI总线和用户设备提供操作接口,协调PCI总线信号和用户设备接口信号,使用户设备能够按照PCI总线的规范进行数据的传输。本文设计了一个适用于CMOS图象处理的PCI目标控制器,具有较强的通用性。

1控制器的顶层设计

PCI总线目标设备在总线传输中处于被动地位,它不会申请对总线的使用权。当PCI总线上的某一主设备发起对本地资源的访问时,整个控制逻辑的建立和数据传输的过程都是通过目标控制器实现的。

图1目标控制器顶层结构

PCI系统中,目标设备在地址周期内响应总线主设备的传输要求,并配合主设备完成整个数据传输。图1为目标控制器的详细结构图。

本设计将目标控制器按照功能分为几个功能模块实现,即命令解码器、状态机、FIFO类型目标接口和寄存器型目标接口。命令解码模块和状态机构成目标控制器的控制部分,PCI主设备发起某类型的操作,目标控制器在地址周期内解析相应的地址和命令信息。在解析地址确定为本次操作的目标设备后,目标控制器会启动目标设备状态机根据当前解码的信息进行一系列的控制操作。FIFO类型通道用于大批量的数据传输,可将本地存储器块挂接在该类型的数据通道上;寄存器类型接口用于数据量小的数据传输,该接口的后面可以挂接配置寄存器和一些本地功能设备的控制/状态寄存器块。这样,PCI总线上的主设备既可以访问到本地的存储器设备也可以访问本地的寄存器。下面从目标控制器的数据路径和控制路径分别进行论述。

2控制模块实现

目标控制器的控制由两部分完成,命令解码器和目标状态机。命令解码器解码来自PCI总线上的地址命令信息作为目标状态机的输入,状态机鉴于此输入执行相应的操作。

(1)命令解码器:PCI总线主设备在地址周期内通过命令数据线(C/BE#)设置不同的编码可以发起以下的操作,I/O读写、存储器读写、配置读写、存储器行读/多行读和存储器写及使无效。

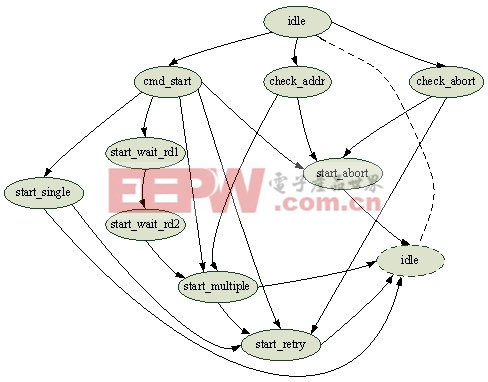

(2)目标状态机[3]:对于PCI总线上传来的信号,状态机根据命令解码器的解码信息来控制总线控制器进行相应的操作。如果地址信息不正确或者本地的设备正忙于存取数据,状态机会向PCI总线上发起本次操作的主设备回应目标丢弃或目标重试。目标状态机的具体设计,如图2所示。

图2目标设备接口状态机

状态机共分为10个状态,下面对每个状态的意义及状态跳转条件的详细说明:

目标空闲(idle):当PCI总线有新的命令但控制器正忙于未完成的数据传输或寄存器配置时,状态机跳转到check_abort;控制器空闲但寄存器内有记录的未完成的读操作,状态机跳转到check_addr;PCI总线上有数据传输要求而又未出现上面的两种情况,状态机跳转至cmd_start。

启动命令解码(cmd_start):满足放弃条件如奇偶校验错误、强制放弃等条件时,状态机跳转至start_abort;不满足放弃条件,若目标设备没有突发传输能力,状态机跳转至start_single,若目标设备有突发传输能力且主设备发起的是写命令,状态机跳转至start_multiple,如果目标设备有突发传输能力且主设备发起的是延迟读命令,状态机跳至start_retry;上述情况均未发生,状态机跳转至start_wait_rd1。

检查地址匹配(check_addr):满足放弃条件如奇偶校验错误、强制放弃等条件时,状态机跳转至start_abort;如果地址与之前的请求地址一致,对目标设备进行延迟读,状态机跳转至start_multiple;如果地址不一致状态机跳转至start_retry。

放弃条件检测(check_abort):满足放弃条件如奇偶校验错误、强制放弃等条件时,状态机跳转至start_abort;不满足条件,状态机转至start_retry。

读等待状态1(start_wait_rd1):如果FIFO中有了待传输的数据,状态机跳转至start_wait_rd2;否则一直等待在状态start_wait_rd1。

读等待状态2(start_wait_rd2):FIFO中已经有了所要读取的数据,状态机跳转至start_multiple。

目标设备放弃(start_abort):一直维持该状态直到主设备声明传输结束,状态机转至idle。

单数据传输(start_single):如果主设备声明最后一个数据传输,状态机跳转至idle;如果主设备继续对该目标设备进行读写操作,状态机跳转至start_retry。

数据突发传输(start_multiple):如果剩下最后一个字节传输,状态机跳转到idle;如果地址信息无效或地址越界,状态机跳转到start_retry;如果接收FIFO几乎满了而PC

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于DSP的PCI驱动程序开发 (04-08)