基于PXA255设计的图像采集传输系统

|

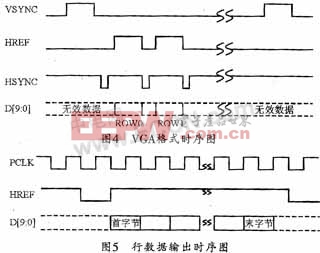

3.2 FPGA与ARM的数据交换

FPGA内部用一个8 KByte双口SRAM作为图像存储区。为了实现图像数据的实时采集与处理,应使图像数据的采集与外部图像数据的读取同时进行。因此本系统采用双缓存结构。实现方法是把8 KB的SRAM划分成两个大小为4 KB的SRAM(设为SRAM1和SRAM2),每片SRAM一次存储六行图像数据。这样,在同一时刻,一片可用于存储图像数据,另一片可用于外部ARM对图像数据的读取。两块SRAM存储区乒乓式切换。当图像数据写满SRAM1时,FPGA向ARM发送一个中断信号,之后,ARM响应中断并读取SRAM1中的图像数据,同时将其写入到SDRAM中。之后,图像传感器的数据将写入SRAM2,当图像数据写满SRAM2时,FPGA也向ARM发送一个中断信号。ARM响应中断并读取SRAM2中的图像数据.同时将其写人到SDRAM中。之后,图像传感器的数据将再次写入SRAM1。

3.3 以太网数据传输的实现

为实现图像数据的网络传输,本系统基于PXA255开发了UDP/IP协议实现程序,以将图像数据存储在SDRAM中。一个完整的数据帧格式包括以太网头、IP头、UDP头和一行图像数据,其系统工作流程图见图6所示。上电后,系统将等待FPGA中断,如果中断产生,则由PXA255读取FPGA中的数据并写到SDRAM中。然后判断是否读完一帧图像数据,若读完,则发送UDP包,并将图像数据通过以太网发送到上位机,否则继续等待FPGA中断。

|

4 结束语

本文介绍了用ARM和FPGA实现的一个实时图像采集传输系统的设计方案,本系统设计方案采用FPGA技术来为作物识别、杂草识别等图像处理算法的实时实现提供了平台。

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)