Xilinx FPGA的嵌入式系统开发过程

摘要:围绕Xilinx公司FPGA中的MicroBlaze软核微处理器,对其体系结构、设计流程和相关开发工具进行了详细介绍,并且通过一个实例说明了以MicroBlaze软核处理器为内核的嵌入式系统的开发过程。

关键词:FPGA;MicroBlaze;嵌入式设计

引言

随着FPGA技术的迅速发展,可编程片上系统(SOPC)作为一种特殊的嵌入式微处理器系统,融合了SoC和FPGA各自的优点,并具备软硬件在系统可编程、可裁减、可扩充、可升级的功能,已逐渐成为一个新兴的技术方向。SOPC的核心是在FPGA上实现的嵌入式微处理器核,目前主要有Xilinx公司集成的32位软核MicroBlaze,32位PowerPC系列处理器硬核PowerPC405、PowerPCA40,ARM公司的Cortex-A9,以及Altera公司的Nios系列微处理器软核等。本文主要介绍Xilinx公司的MicroBlaze软核结构,对其体系结构、设计流程和相关开发工具一一进行介绍,并在实际的无线电监测系统中采用此方案,构建了一个小型化、智能化、网络化的软件无线电处理平台。

1 MicroBlaze处理器结构

MicroBlaze软核处理器是可配置的精简指令集(RISC)32位CPU,该RISC核针对Xilinx公司的FPGA芯片进行了优化。设计人员可以根据设计定制处理器的可选配置,根据版本的不同,配置不同的选项。该软核处理器具有以下几个方面的特征:

◆32个32位通用寄存器;

◆32位3个操作数的指令字,指令字有2种寻址模式;

◆分离的32位地址总线和数据总线;

◆具有高速的指令和数据缓存,3级和5级流水线操作;

◆灵活的总线结构,支持LMB、OPB、PLB、XCL、FSL片上总线接口等,新推出的系列还支持AXI总线接口;

◆支持MMU存储管理、FPU浮点单元、高速缓存、异常处理和调试逻辑等可根据性能需求和逻辑区域成本任意裁减的高级特性。

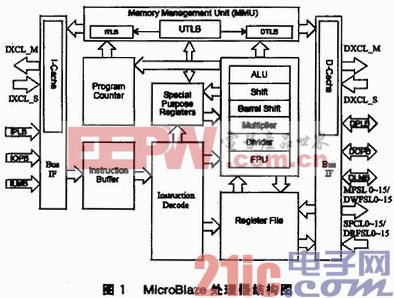

MicroBlaze的这些特性极大地扩展了其应用范围,MicroBlaze处理器的内核仍在不断更新之中,目前使用的版本MicroBlaze v7.1,其内部架构如图1所示。

图1中MicroBlaze处理器的外部接口定义如下:

①DPLB(Data Processor Local Bus)、DOPB(Data On—chip Peripheral Bus);数据接口,处理器本地总线,用于处理器与片内的设备数据交换。

②IPLB(Instruction Processor Local Bus)、IOPB(Instruction On-Chip Peripheral Bus):指令接口,用于指令读取通道。

③DLMB(Data Local Memory Bus):数据接口,本地存储器总线,用于高速数据交换。

④ILMB(Instruction Local Memory Bus);指令接口,实现高速指令读取。

⑤MFSL0~15(Main Fast Simple Link):FSL主设备数据接口,提供点对点数据通道;SFSL0~15(Slave FastSimple Link):FSL从设备点对点数据接口。

⑥DWFSL0~15:FSL主设备直接连接接口;DRFSL0~15:FSL从设备直接连接接口;

⑦IXCL(Instruction side Xilinx CacheLink interface)和DXCL(Data side Xilinx CacheLink interface):分别为指令高速缓存接口和数据高速缓存接口。

2 EDK工具开发流程

Xilinx公司嵌入式开发套件工具EDK(Embedded Development Kit)为用于开发基于MieroBlaze软核和PowerPC硬核处理器的SOPC系统提供了一个很好的工具平台。Xilinx公司的EDK工具主要包含:Xilinx Platform Studio(XPS)人机界面、嵌入式系统工具套件、嵌入式处理IP核、Platform Studio SDK(Software Development Kit,SDK)。XPS提供下面的特性:

◆能够添加核,编辑核参数,进行总线和信号连接,产生MHS文件;

◆能够产生和修改MSS文件;

◆支持Xilinx底层所有工具;

◆能够产生和观察系统块图和设计报告;

◆多用户软件应用支持;

◆项目管理;

◆过程和工具流程依赖管理。

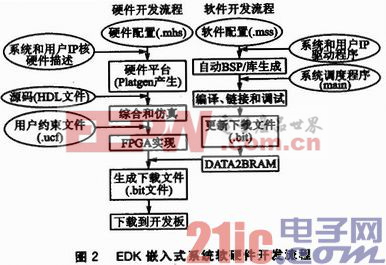

一个完整的嵌入式处理器系统设计通常包括3个部分:硬件系统的构建、软件系统及存储器映射、应用程序开发。

硬件系统的构建是指设计人员根据应用的需要而使用Xilinx的技术建立灵活的嵌入式处理子系统。硬件平台是由一个或多个处理器或外设连接到处理器总线构成的,EDK通过微处理器硬件规范(Microprocessor Hardware Specification,MHS)文件记录硬件平台信息。

软件系统及存储器映射是由软件驱动和用于建立应用程序的操作系统组成的。所建立的软件映像文件只包含用户所使用到的一部分Xili nx的库。EDK通过微处理器软件规范(Microprocessor Software Spectifcation,MSS)记录软件平台信息。设计人员可以在软件平台运行多个应用程序。

MHS和MSS数据文件定义了嵌入式系统,其开发流程如图2所示。

3.1 系统的硬件组成

本文以某智能无线电监测管控系统为例,采用基于FPGA的SOPC技术,选用的实验平台为Xilinx公司的XCAVSX35 FPGA开发平台。图3表示的是系统中嵌入式处理器的硬件组成,这些硬件除A/D转换模块、干扰机和控制中心外,都集成在一块FPGA评估板上。系统以带有32位Micro Blaze软核的FPGA作为控制中心,处理经A/D变换后的侦察信号数据,然后通过以太网将数据传送到控制中心,并从控制中心传回控制参数DDR_SDRAM作为片外存储器,用来弥补微处理器内部存储器容量小的缺点;CF卡存储系统软硬件的bit文件和网络配置文件;串口用来控制具有远程控制功能的侦察接收机,也可在调试时输出系统的运行信息。本文设计的嵌入式系统的各功能部件在FPGA内部都以IP核的形式构建并连接,包括DDC和FFT自定义的IP核,它们分别以PLB总线和FSL总线挂接在MicroBlaze上,较好地满足了智能无线电监测管控系统的硬件设计需求。

FPGA MicroBlaze 嵌入式设计 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)