基于PCI总线的高速CCD图像存储系统设计

时间:02-05

来源:互联网

点击:

必须将64bit数据进行位并转换,变成32bit传输。本系

统设计在FPGA内部将数据的高32bit和低32bit分别送入二选一BUSMUX的输入端,系统时钟的电平选

择数据输出。64bit数据转化成32bit数据传输,但数据率变成原来的两倍(30M/s)。

数据采集存储

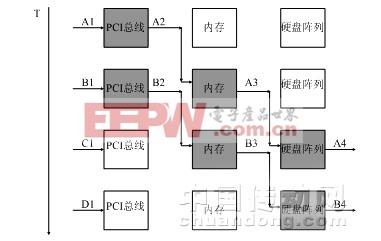

对于整个系统来说,存储系统的持续存储速度是个至关重要的参数。数据的采集存储采用微机为主体,在其PCI总线上挂载一块SCSI的接口卡和9054接口卡,9054接口卡用于数据采集,SCSI接口卡上挂载两个SCSI硬盘,组成RAID-0的硬盘阵列,这样可以大大提高硬盘的持续存储速度。利用PCI9054进行数据采集时,数据的传输路径为:PCI总线-内存-硬盘阵列。现有两种传输方案可供选择:第一种为单线采集存储,显然,这种方案会降低数据的的采集速度。本系统选用第二种方案:流水线存储,如图2所示。理论上,流水线方式的数据采集速度应该是单线采集的两倍。

图2流水线存储时序示意图

- 用双端口RAM实现与PCI总线接口的数据通讯(05-06)

- 基于PCI总线和DSP芯片的图像处理平台的硬件设计(07-06)

- 基于DSP和PCI总线的通用数字信号处理系统(11-13)

- 一种基于PCI总线和DSP技术的虚拟仪器设计(03-16)

- 基于Linux平台的天气雷达高速数据采集系统设计(03-13)

- 基于DSP与PC机的PCI总线高速数据传输 (07-08)